# SYNAPTIC PLASTICITY IN NEUROMORPHIC SYSTEMS

EDITED BY: Christian Mayr, Sadique Sheik, Chiara Bartolozzi and Elisabetta Chicca

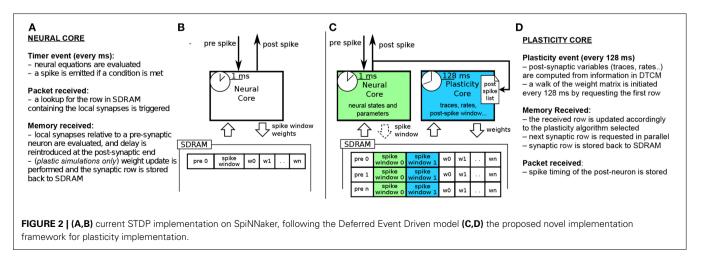

**PUBLISHED IN: Frontiers in Neuroscience**

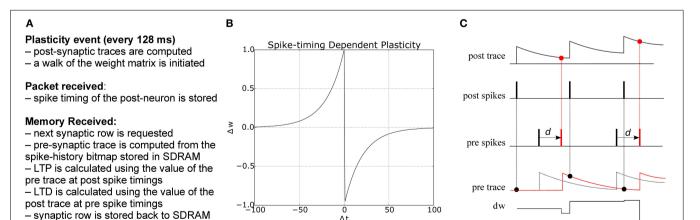

#### Frontiers Copyright Statement

© Copyright 2007-2016 Frontiers Media SA. All rights reserved.

All content included on this site, such as text, graphics, logos, button icons, images, video/audio clips, downloads, data compilations and software, is the property of or is licensed to Frontiers Media SA ("Frontiers") or its licensees and/or subcontractors. The copyright in the text of individual articles is the property of their respective authors, subject to a license granted to Frontiers.

The compilation of articles constituting this e-book, wherever published, as well as the compilation of all other content on this site, is the exclusive property of Frontiers. For the conditions for downloading and copying of e-books from Frontiers' website, please see the Terms for Website Use. If purchasing Frontiers e-books from other websites or sources, the conditions of the website concerned apply.

Images and graphics not forming part of user-contributed materials may not be downloaded or copied without permission.

Individual articles may be downloaded and reproduced in accordance with the principles of the CC-BY licence subject to any copyright or other notices. They may not be re-sold as an e-book.

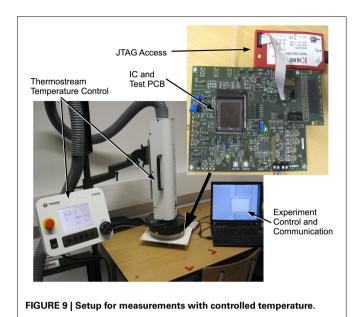

As author or other contributor you grant a CC-BY licence to others to reproduce your articles, including any graphics and third-party materials supplied by you, in accordance with the Conditions for Website Use and subject to any copyright notices which you include in connection with your articles and materials.

All copyright, and all rights therein, are protected by national and international copyright laws.

The above represents a summary only. For the full conditions see the Conditions for Authors and the Conditions for Website Use.

ISSN 1664-8714 ISBN 978-2-88919-877-1 DOI 10.3389/978-2-88919-877-1

#### **About Frontiers**

Frontiers is more than just an open-access publisher of scholarly articles: it is a pioneering approach to the world of academia, radically improving the way scholarly research is managed. The grand vision of Frontiers is a world where all people have an equal opportunity to seek, share and generate knowledge. Frontiers provides immediate and permanent online open access to all its publications, but this alone is not enough to realize our grand goals.

#### **Frontiers Journal Series**

The Frontiers Journal Series is a multi-tier and interdisciplinary set of open-access, online journals, promising a paradigm shift from the current review, selection and dissemination processes in academic publishing. All Frontiers journals are driven by researchers for researchers; therefore, they constitute a service to the scholarly community. At the same time, the Frontiers Journal Series operates on a revolutionary invention, the tiered publishing system, initially addressing specific communities of scholars, and gradually climbing up to broader public understanding, thus serving the interests of the lay society, too.

#### **Dedication to Quality**

Each Frontiers article is a landmark of the highest quality, thanks to genuinely collaborative interactions between authors and review editors, who include some of the world's best academicians. Research must be certified by peers before entering a stream of knowledge that may eventually reach the public - and shape society; therefore, Frontiers only applies the most rigorous and unbiased reviews.

Frontiers revolutionizes research publishing by freely delivering the most outstanding research, evaluated with no bias from both the academic and social point of view. By applying the most advanced information technologies, Frontiers is catapulting scholarly publishing into a new generation.

#### **What are Frontiers Research Topics?**

1

Frontiers Research Topics are very popular trademarks of the Frontiers Journals Series: they are collections of at least ten articles, all centered on a particular subject. With their unique mix of varied contributions from Original Research to Review Articles, Frontiers Research Topics unify the most influential researchers, the latest key findings and historical advances in a hot research area! Find out more on how to host your own Frontiers Research Topic or contribute to one as an author by contacting the Frontiers Editorial Office: **researchtopics@frontiersin.org**

# SYNAPTIC PLASTICITY IN NEUROMORPHIC SYSTEMS

**Topic Editors:**

Christian Mayr, Technische Universität Dresden, Germany Sadique Sheik, University of California, San Diego, USA Chiara Bartolozzi, Istituto Italiano di Tecnologia, Italy Elisabetta Chicca, Bielefeld University, Germany

One of the most striking properties of biological systems is their ability to learn and adapt to ever changing environmental conditions, tasks and stimuli. It emerges from a number of different forms of plasticity, that change the properties of the computing substrate, mainly acting on the modification of the strength of synaptic connections that gate the flow of information across neurons.

Plasticity is an essential ingredient for building artificial autonomous cognitive agents that can learn to reliably and meaningfully interact with the real world. For this reason, the neuromorphic community at large has put substantial effort in the design of different forms of plasticity and in putting them to practical use. These plasticity forms comprise, among others, Short Term Depression and Facilitation, Homeostasis, Spike Frequency Adaptation and diverse forms of Hebbian learning (e.g. Spike Timing Dependent Plasticity).

This special research topic collects the most advanced developments in the design of the diverse forms of plasticity, from the single circuit to the system level, as well as their exploitation in the implementation of cognitive systems.

**Citation:** Mayr, C., Sheik, S., Bartolozzi, C., Chicca, E., eds. (2016). Synaptic Plasticity in Neuromorphic Systems. Lausanne: Frontiers Media. doi: 10.3389/978-2-88919-877-1

# Table of Contents

#### 05 Editorial: Synaptic Plasticity for Neuromorphic Systems

Christian G. Mayr, Sadigue Sheik, Chiara Bartolozzi and Elisabetta Chicca

#### **Chapter 1: Plasticity Operating on Sensor Input**

# 08 Racing to learn: statistical inference and learning in a single spiking neuron with adaptive kernels

Saeed Afshar, Libin George, Jonathan Tapson, André van Schaik and Tara J. Hamilton

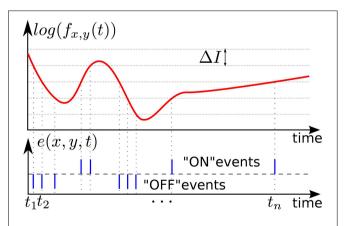

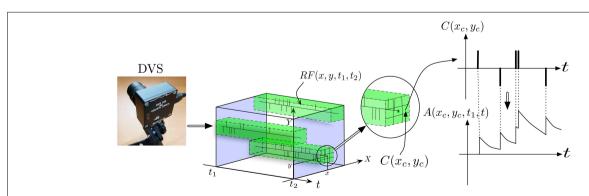

#### 26 Spatiotemporal features for asynchronous event-based data

Xavier Lagorce, Sio-Hoi leng, Xavier Clady, Michael Pfeiffer and Ryad B. Benosman

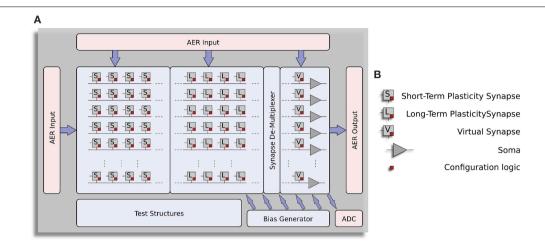

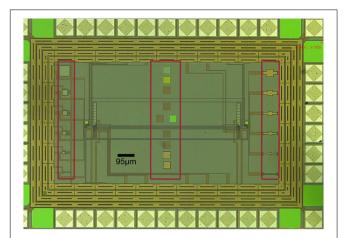

# 39 A reconfigurable on-line learning spiking neuromorphic processor comprising 256 neurons and 128K synapses

Ning Qiao, Hesham Mostafa, Federico Corradi, Marc Osswald, Fabio Stefanini, Dora Sumislawska and Giacomo Indiveri

#### **Chapter 2: Large Scale Hardware for Plasticity**

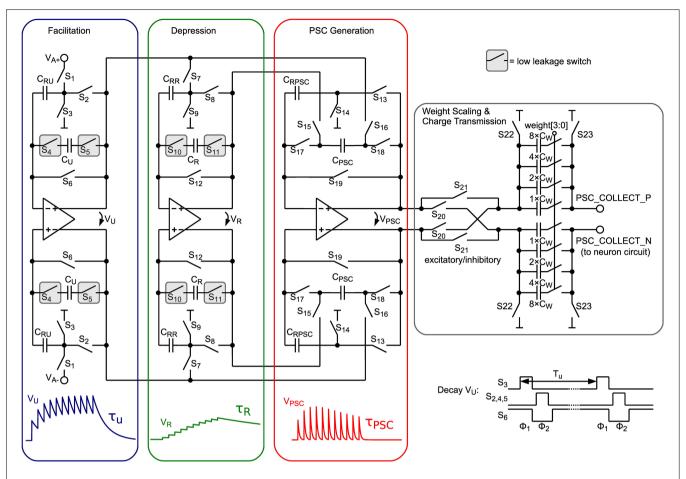

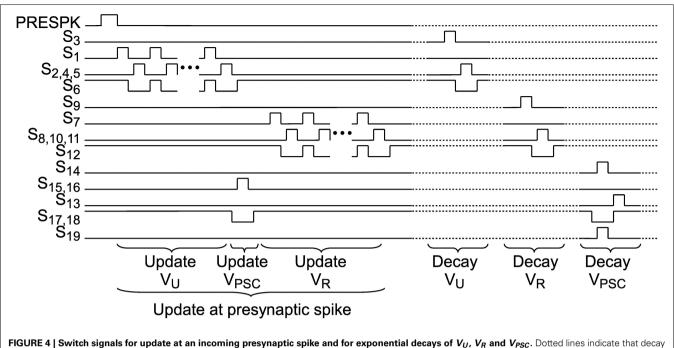

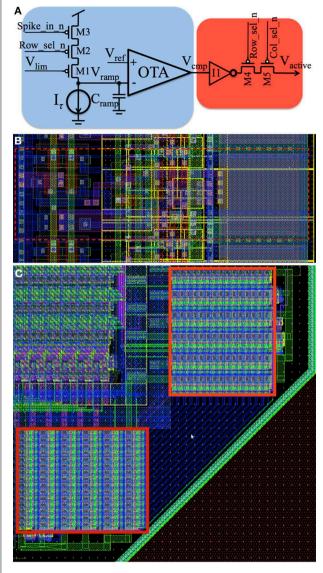

#### 56 Switched-capacitor realization of presynaptic short-term-plasticity and stoplearning synapses in 28 nm CMOS

Marko Noack, Johannes Partzsch, Christian G. Mayr, Stefan Hänzsche, Stefan Scholze, Sebastian Höppner, Georg Ellguth and Rene Schüffny

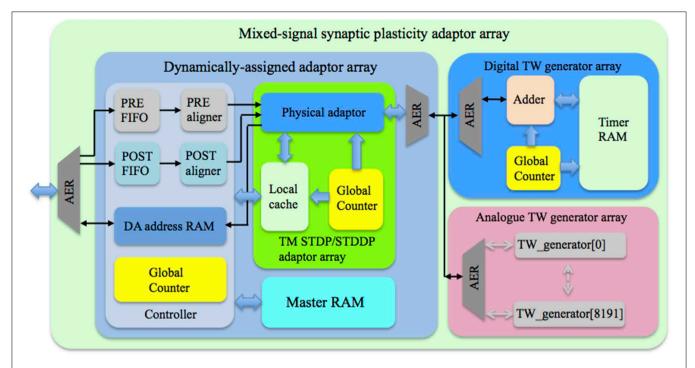

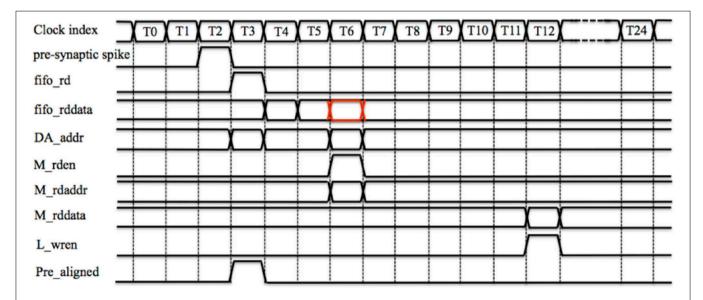

# 70 A neuromorphic implementation of multiple spike-timing synaptic plasticity rules for large-scale neural networks

Runchun M. Wang, Tara J. Hamilton, Jonathan C. Tapson and André van Schaik

#### **Chapter 3: Digital Implementations of Plasticity**

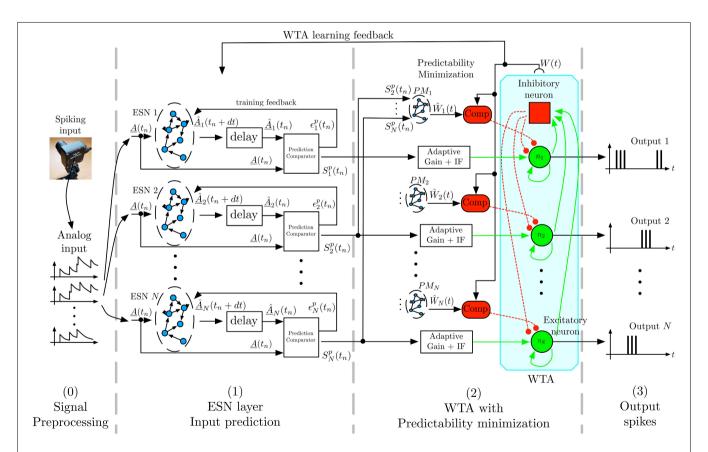

# 87 A framework for plasticity implementation on the SpiNNaker neural architecture

Francesco Galluppi, Xavier Lagorce, Evangelos Stromatias, Michael Pfeiffer, Luis A. Plana, Steve B. Furber and Ryad B. Benosman

#### 107 Reducing the computational footprint for real-time BCPNN learning

Bernhard Vogginger, René Schüffny, Anders Lansner, Love Cederström, Johannes Partzsch and Sebastian Höppner

#### **Chapter 4: Memristive Plasticity**

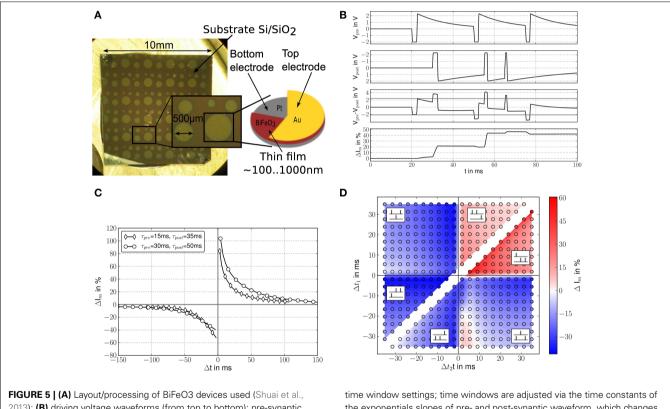

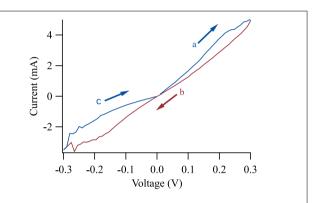

#### 123 Plasticity in memristive devices for spiking neural networks

Sylvain Saïghi, Christian G. Mayr, Teresa Serrano-Gotarredona, Heidemarie Schmidt, Gwendal Lecerf, Jean Tomas, Julie Grollier, Sören Boyn, Adrien F. Vincent, Damien Querlioz, Selina La Barbera, Fabien Alibart, Dominique Vuillaume, Olivier Bichler, Christian Gamrat and Bernabé Linares-Barranco

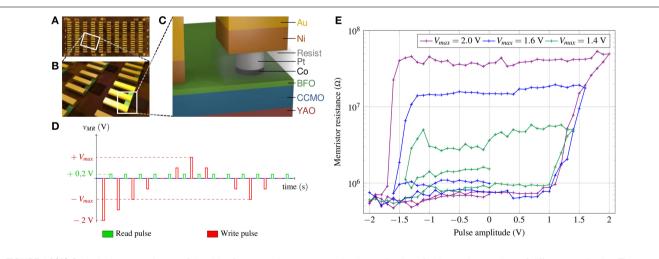

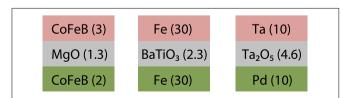

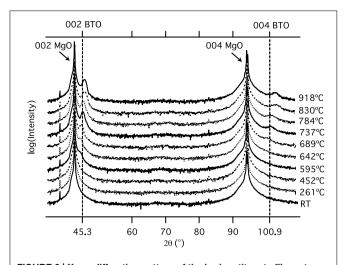

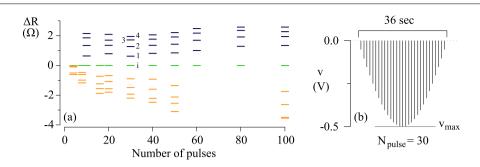

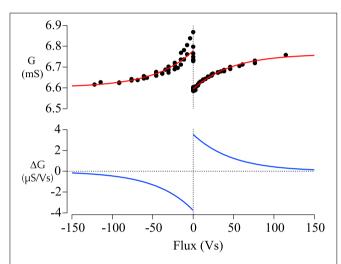

- 139 Tunnel junction based memristors as artificial synapses

- Andy Thomas, Stefan Niehörster, Savio Fabretti, Norman Shepheard, Olga Kuschel, Karsten Küpper, Joachim Wollschläger, Patryk Krzysteczko and Elisabetta Chicca

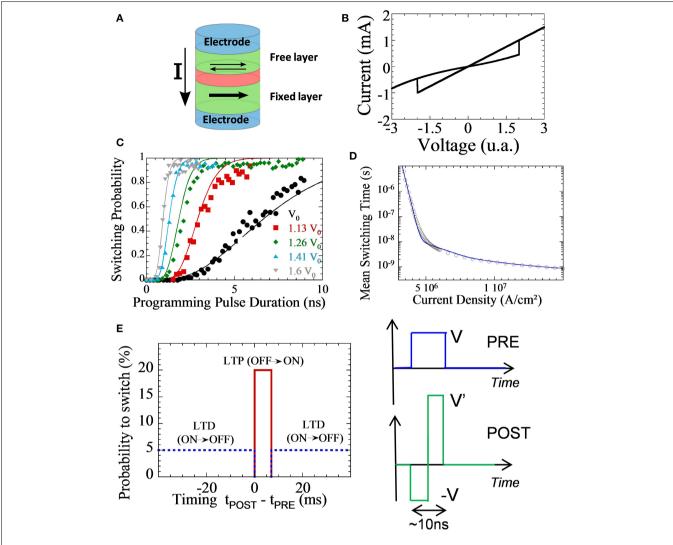

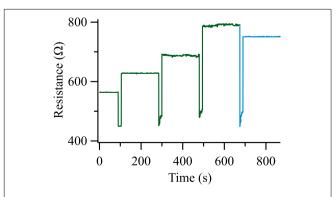

- 148 A 2-transistor/1-resistor artificial synapse capable of communication and stochastic learning in neuromorphic systems

- Zhongqiang Wang, Stefano Ambrogio, Simone Balatti and Daniele Ielmini

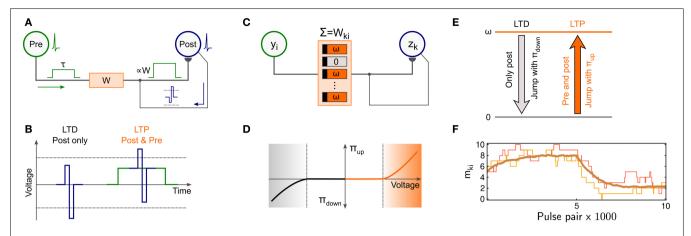

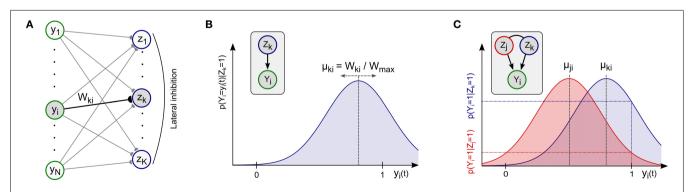

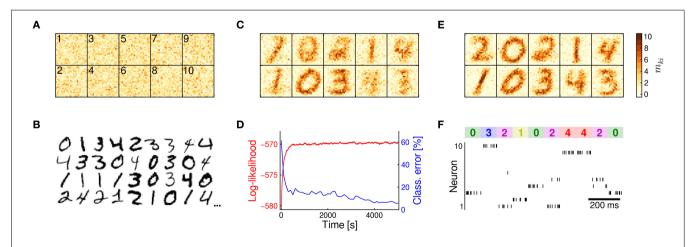

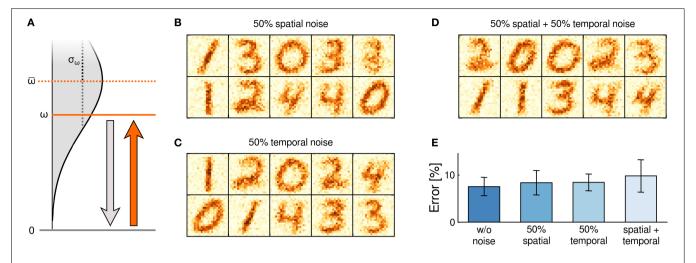

- 159 A compound memristive synapse model for statistical learning through STDP in spiking neural networks

- Johannes Bill and Robert Legenstein

# Editorial: Synaptic Plasticity for Neuromorphic Systems

Christian G. Mayr<sup>1\*</sup>, Sadique Sheik<sup>2</sup>, Chiara Bartolozzi<sup>3</sup> and Elisabetta Chicca<sup>4</sup>

<sup>1</sup> Chair of Highly-Parallel VLSI-Systems and Neuromorphic Circuits, Technische Universität Dresden, Dresden, Germany, <sup>2</sup> BioCircuits Institute, University of California, San Diego, San Diego, CA, USA, <sup>3</sup> iCub Facility, Istituto Italiano di Tecnologia, Genova, Italy, <sup>4</sup> Cognitive Interaction Technology - Center of Excellence, Faculty of Technology, Bielefeld University, Bielefeld, Germany

Keywords: synaptic plasticity, neuromorphic engineering, memristive plasticity, plasticity circuits, digital plasticity, high-density plasticity, plasticity for sensor data, learning feature extraction

The Editorial on the Research Topic

#### Synaptic Plasticity for Neuromorphic Systems

Brain plasticity serves animals in a wide range of vital functions. It assists them in adapting their behavior to the surroundings, in learning new strategies for optimizing a certain reward-seeking policy for their survival or in adjusting motor activity through sensory feedback. Thus, plasticity is an essential ingredient for building artificial autonomous systems that can cope with the real world. In order to build these systems, neuromorphic design labs actively investigate and develop various circuit implementations of plasticity. This research topic collects a comprehensive snapshot of this work. A number of manuscripts published in this topic study the interplay between stochasticity and plasticity (Afshar et al.; Bill and Legenstein; Lagorce et al.; Qiao et al.). Plasticity here acts in a stochastic fashion or extracts features from stochastic sensor data. The current push toward higher complexity/scale in neuromorphic devices can also be observed in plasticity implementations (Qiao et al.; Wang et al.; Noack et al.). Due to advantageous technology scaling and reproducibility, digital implementations of neuromorphic plasticity are gaining popularity (Galluppi et al.; Vogginger et al.). The collection of articles in this topic is rounded out by articles on plasticity in novel nano-scale technologies (Saighi et al.; Thomas et al.; Wang et al.; Bill and Legenstein).

#### **OPEN ACCESS**

#### Edited by:

Timothy K. Horiuchi, The University of Maryland, USA

#### Reviewed by:

Theodore Yu, Texas Instruments Inc., USA

#### \*Correspondence:

Christian Mayr christian.mayr@tu-dresden.de

#### Specialty section:

This article was submitted to Neuromorphic Engineering, a section of the journal Frontiers in Neuroscience

Received: 27 January 2016 Accepted: 27 April 2016 Published: 19 May 2016

#### Citation

Mayr CG, Sheik S, Bartolozzi C and Chicca E (2016) Editorial: Synaptic Plasticity for Neuromorphic Systems. Front. Neurosci. 10:214. doi: 10.3389/fnins.2016.00214

#### 1. STOCHASTICITY AND PLASTICITY

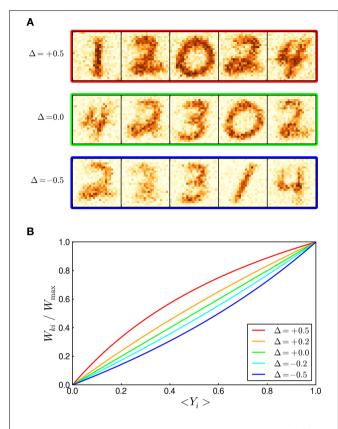

One topic of interest in recent publications is the interaction between stochasticity and synaptic dynamics. Wang et al. introduces a stochastic synapse cell constructed with a memristor and two transistors. Bill and Legenstein show that stochastic synapses can provide graded responses from binary-valued synapses, aiding convergence in learning tasks. Stochasticity in conjunction with plasticity can also aid error tolerance. For instance, the stochastic synapse model of Bill and Legenstein can learn handwritten digits with high fidelity in the presence of significant device deviations and noise. The statistical inference in Afshar et al. actually uses deviations between individual dendrites. The visual feature extraction in Lagorce et al. operates on a high-dimensional projection of the input space through a recurrent neural network, benefitting from deviations across elements. A more conventional error-compensation approach is taken in Qiao et al., where a network counterbalances for deviations through a learned aggregate of individual neuronal responses.

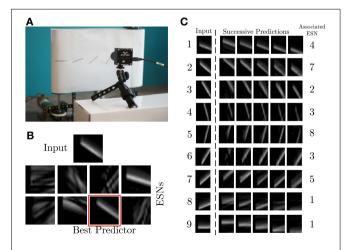

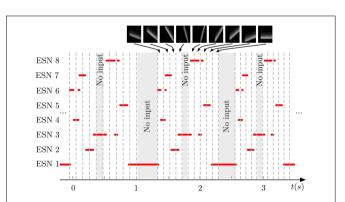

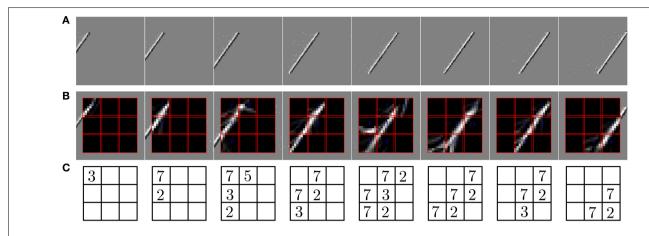

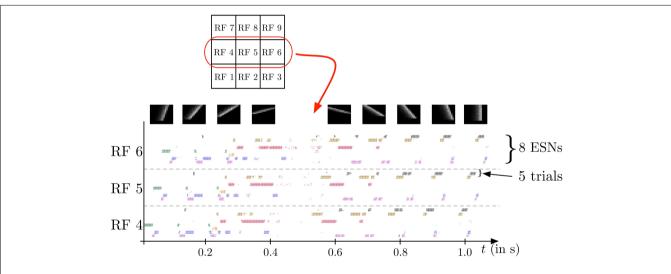

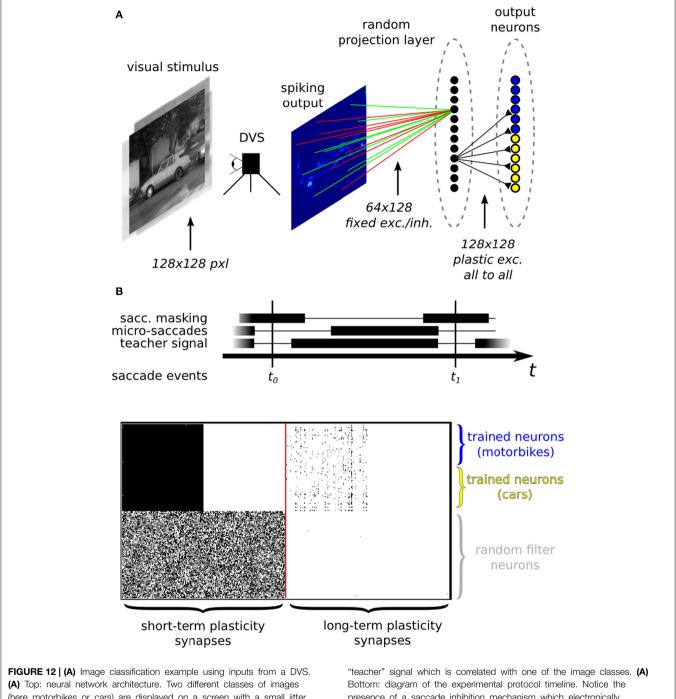

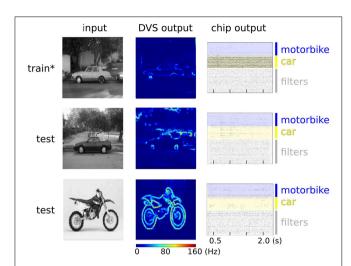

#### 2. PLASTICITY OPERATING ON SENSOR DATA

The above mentioned Qiao et al. and Lagorce et al. also represent examples of processing and plasticity operating directly on spiking input. In fact, typical tasks that would be amenable to

a neuromorphic solution have traditionally used non-spiking input, such as image processing applications exclusively using image frames (Henker et al., 2007). Due to these incompatible representations (e.g., continuous time vs. discrete time, spikes vs. scalar values), there has not been much synergy between neuromorphic and traditional sensor processing, thus potentially missing some novel approaches in both fields. However, the two are growing closer together as sensors with spiking output are becoming more widely available in such diverse areas as vision (Delbruck, 2008) or audition (Liu et al., 2010). In addition to the plastic sensory processing in Qiao et al. and Lagorce et al., the statistical inference of Afshar et al. could also be employed for sensory processing, as it is geared toward the temporal patterns of multiple input spike trains.

# 3. DIGITAL IMPLEMENTATIONS OF PLASTICITY

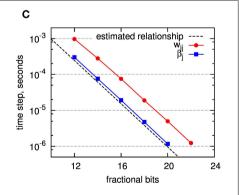

Neuromorphic engineering was envisioned as analog VLSI circuits, due to the similarity between the current across CMOS devices in subthreshold and across neurons ion channels. However, digital circuits benefit significantly more from technology scaling and low-power advances in deep-submicron nodes, making them attractive for neuromorphic implementations. Specifically, plasticity allows fixed, reproducible-function digital circuits to add adaptability and variation to their behavior. Galluppi et al. present a framework for plasticity implementation on a programmable digital neuromorphic system, SpiNNaker. Vogginger et al. discuss a computational optimization of a powerful learning rule, outlining an efficient implementation in a synthesized or programmable digital neuromorphic system. Afshar et al. present an FPGA implementation of a novel neuron model and an accompanying learning rule optimized for digital circuits.

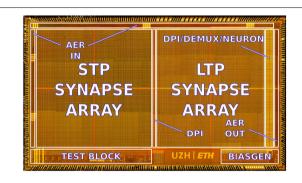

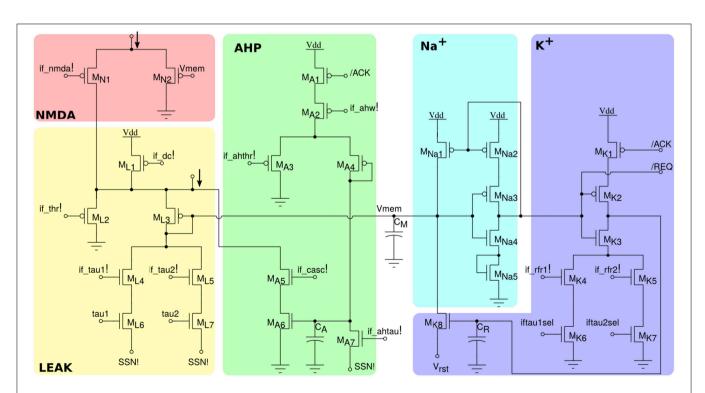

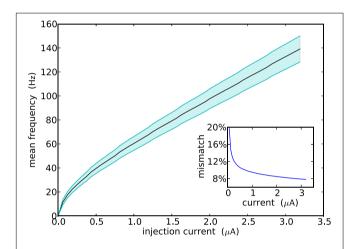

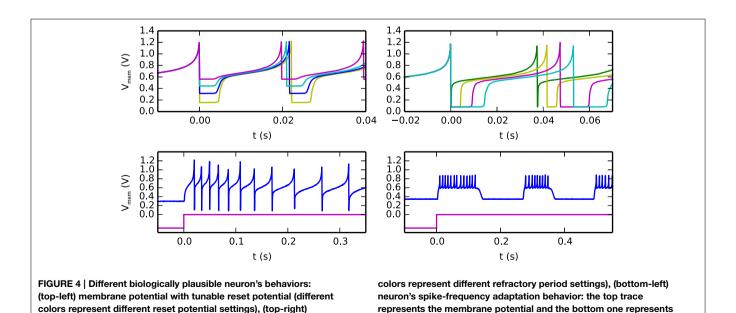

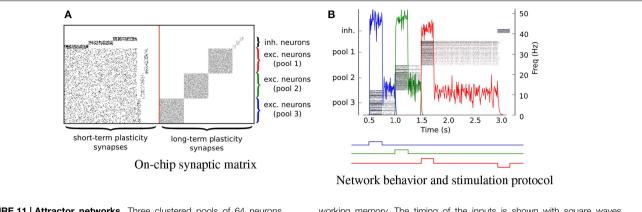

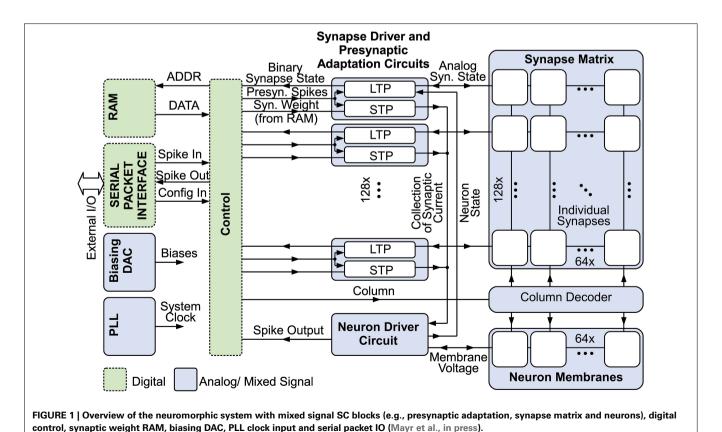

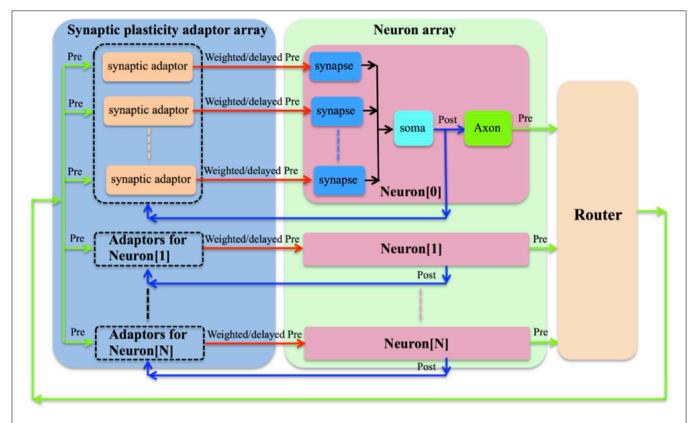

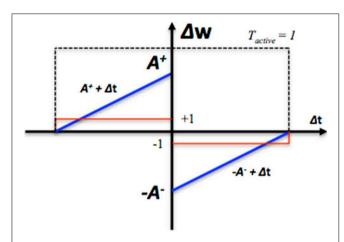

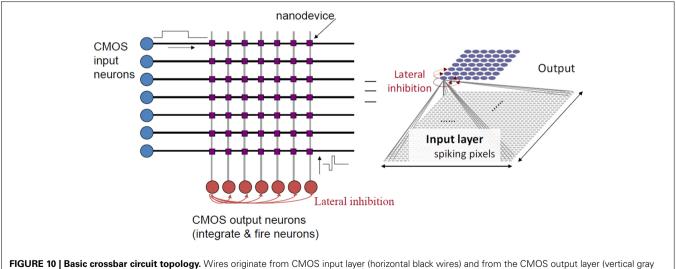

# 4. LARGE SCALE HARDWARE FOR PLASTICITY

Complex real-world applications demand large, computationally capable neural networks. Consequently, there is a drive toward large scale neuromorphic hardware with plasticity. The chip of Qiao et al. is currently one of the largest devices with onchip plasticity (256 neurons, 128k synapses, 180 nm CMOS) that employs the original subthreshold design philosophy. Noack et al. present a switched capacitor implementation of shortand long-term plasticity in 28 nm CMOS that at 3.6  $\times$  3.6  $\mu \rm m^2$  is an order of magnitude smaller than any other plastic CMOS synapse. Other approaches to scaling include Wang et al., which uses a digital time-multiplexed circuit to compute Spike Timing Dependent Plasticity (STDP) for time-multiplexed analog neurons. For large-scale networks, topological considerations also play an increasing role, e.g.,

in terms of which signals a plasticity circuit needs access to (e.g., pre- or post-synaptic) (Noack et al., 2010). A neuron-synapse matrix arrangement seems the obvious choice, but the implementations in this topic explore a variety of other options.

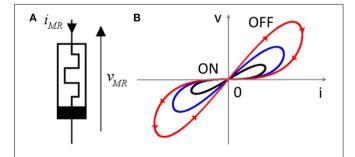

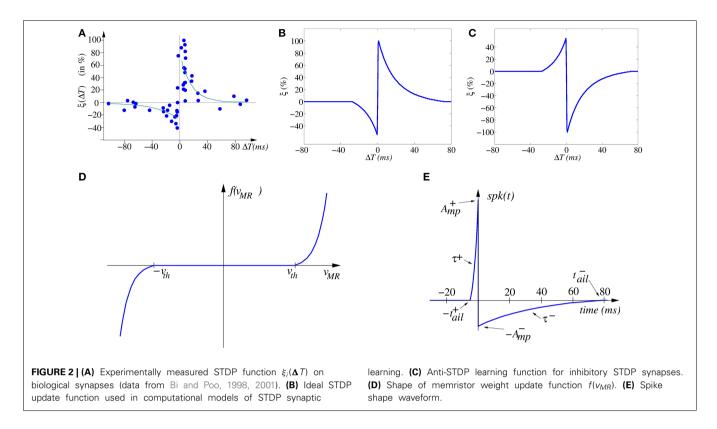

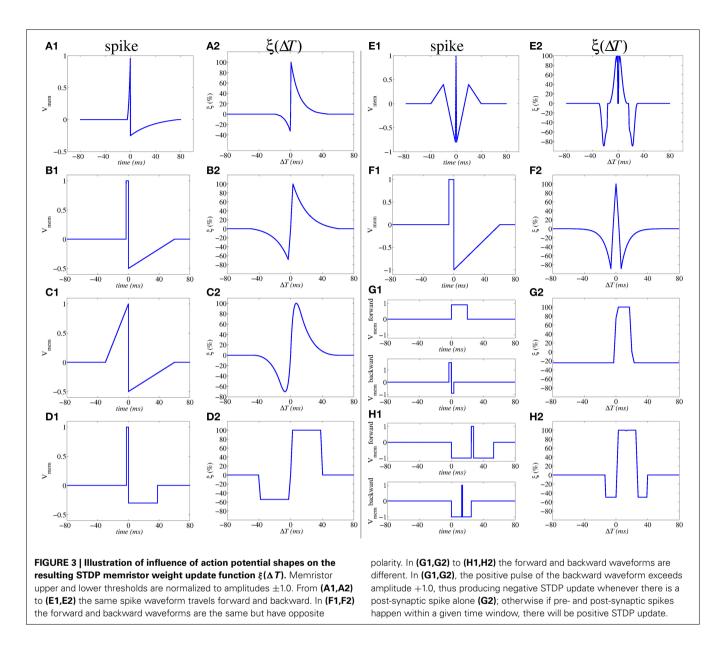

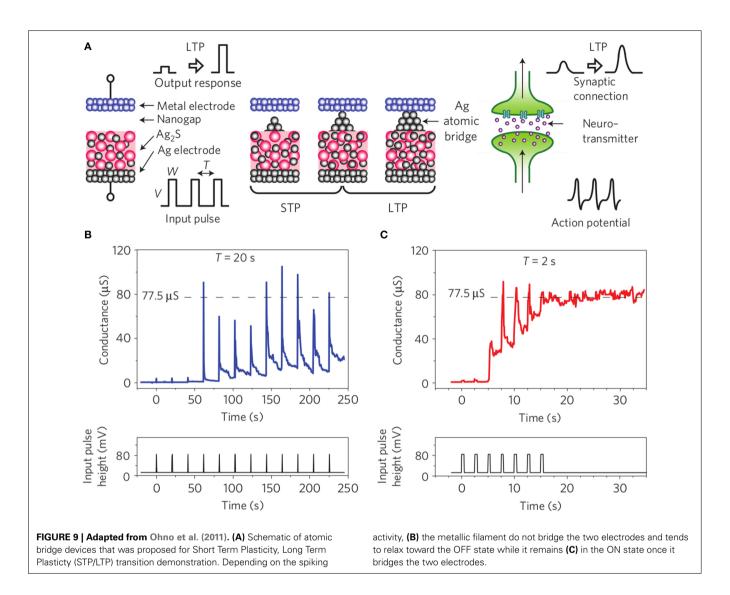

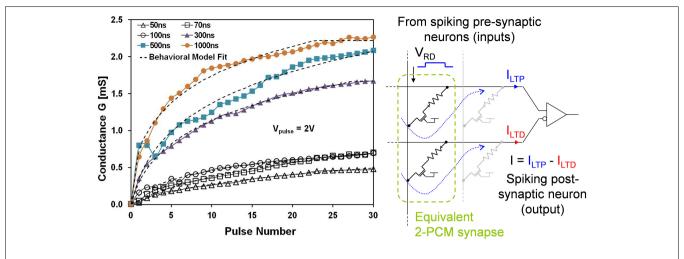

#### 5. MEMRISTIVE PLASTICITY

In terms of emerging technologies, the usage of nanoscale memristors for short- or long term plasticity has seen a large deal of interest since the pioneering work of Jo et al. (2010). Memristors inherently replicate aspects of synaptic plasticity and can combine plasticity, weight storage and weight effect in a single device. Saighi et al. gives an overview of recent developments in this area from a materials and neuromorphic perspective. Thomas et al. investigate tunnel junction based memristors that exhibit STDP-like plasticity. Wang et al. present a synaptic cell composed of memristor plus transistors which endows the synapse with stochastic learning capabilities. Bill and Legenstein introduce a model of an ideal stochastic memristor synapse and investigate its computational properties.

#### 6. SUMMARY

Synaptic plasticity is a crucial ingredient in neuromorphic hardware. It has the potential to contribute to many different fields, such as in the endeavor of building realistic brain models, in biohybrids where the hardware adapts to the biological counterpart or in the construction of truly cognitive systems. This research topic gives an overview of the state-of the art in plasticity circuit design and applications and outlines future research directions.

#### **AUTHOR CONTRIBUTIONS**

CM, EC, CB, and SS all contributed to the compilation of plasticity works described in this editorial and to the writing of the editorial.

#### **ACKNOWLEDGMENTS**

This work was supported by the Excellence Cluster 227 (CITEC, Bielefeld University), the U.S. Office of Naval Research(ONR) under Grant Number N00014-13-1-0205 and the Swiss National Science Foundation under grant number P2EZP2\_155561. This research has received funding from the European Union Seventh Framework Programme (FP7/2007- 2013) under grant agreement no. 269459 (CORONET), no. 612058 (RAMP) and no. 284553 (SICODE). The authors would like to thank all contributors of the Frontiers Special Topic. We wish to acknowledge R. Douglas, G. Indiveri, S. Fusi and F. Stefanini for insightful discussions.

#### **REFERENCES**

- Delbruck, T. (2008). "Frame-free dynamic digital vision," in *Proceedings of the International Symposium on Secure-Life Electronics*, Vol. 1 (Tokyo: University of Tokyo).

- Henker, S., Mayr, C., Schlüssler, J.-U., Schüffny, R., Ramacher, U., and Heittmann, A. (2007). "Active pixel sensor arrays in 90/65nm CMOS-technologies with vertically stacked photodiodes," in *Proceedings IEEE International Image Sensor Workshop IIS07*, (Ogunquit, ME).

- Jo, S. H., Chang, T., Ebong, I., Bhadviya, B. B., Mazumder, P., and Lu, W. (2010). Nanoscale memristor device as synapse in neuromorphic systems. *Nano Lett.* 10, 1297–1301. doi: 10.1021/nl904092h

- Liu, S., van Schaik, A., Minch, B., and Delbruck, T. (2010). "Event-based 64-channel binaural silicon cochlea with q enhancement mechanisms," in Circuits and Systems (ISCAS), Proceedings of 2010 IEEE International Symposium on, (Paris: IEEE).

- Noack, M., Partzsch, J., Mayr, C., Henker, S., and Schuffny, R. (2010). "Biology-derived synaptic dynamics and optimized system architecture for neuromorphic hardware," in *Mixed Design of Integrated Circuits and Systems (MIXDES)*, 2010 Proceedings of the 17th International Conference, (Warsaw).

**Conflict of Interest Statement:** The authors declare that the research was conducted in the absence of any commercial or financial relationships that could be construed as a potential conflict of interest.

Copyright © 2016 Mayr, Sheik, Bartolozzi and Chicca. This is an open-access article distributed under the terms of the Creative Commons Attribution License (CC BY). The use, distribution or reproduction in other forums is permitted, provided the original author(s) or licensor are credited and that the original publication in this journal is cited, in accordance with accepted academic practice. No use, distribution or reproduction is permitted which does not comply with these terms.

# Racing to learn: statistical inference and learning in a single spiking neuron with adaptive kernels

Saeed Afshar<sup>1</sup>\*, Libin George<sup>2</sup>, Jonathan Tapson<sup>1</sup>, André van Schaik<sup>1</sup> and Tara J. Hamilton<sup>1,2</sup>

- <sup>1</sup> Bioelectronics and Neurosciences, The MARCS Institute, University of Western Sydney, Penrith, NSW, Australia

- <sup>2</sup> School of Electrical Engineering and Telecommunications, The University of New South Wales, Sydney, NSW, Australia

#### Edited by:

Chiara Bartolozzi, Italian Institute of Technology, Italy

#### Reviewed by:

Sadique Sheik, University of Zurich, ETH Zurich, Switzerland Mattia Rigotti, IBM Research, USA Stephen Nease, Cognitive Interaction Technology - Center of Excellence Bielefeld, Germany

#### \*Correspondence:

Saeed Afshar, Bioelectronics and Neuroscience, The MARCS Institute, University of Western Sydney, Locked Bag 1797, Penrith, NSW 2751, Australia e-mail: s.afshar@uws.edu.au This paper describes the Synapto-dendritic Kernel Adapting Neuron (SKAN), a simple spiking neuron model that performs statistical inference and unsupervised learning of spatiotemporal spike patterns. SKAN is the first proposed neuron model to investigate the effects of dynamic synapto-dendritic kernels and demonstrate their computational power even at the single neuron scale. The rule-set defining the neuron is simple: there are no complex mathematical operations such as normalization, exponentiation or even multiplication. The functionalities of SKAN emerge from the real-time interaction of simple additive and binary processes. Like a biological neuron, SKAN is robust to signal and parameter noise, and can utilize both in its operations. At the network scale neurons are locked in a race with each other with the fastest neuron to spike effectively "hiding" its learnt pattern from its neighbors. The robustness to noise, high speed, and simple building blocks not only make SKAN an interesting neuron model in computational neuroscience, but also make it ideal for implementation in digital and analog neuromorphic systems which is demonstrated through an implementation in a Field Programmable Gate Array (FPGA). Matlab, Python, and Verilog implementations of SKAN are available at: http://www.uws.edu.au/bioelectronics\_neuroscience/bens/reproducible\_research.

Keywords: spiking neural network, neuromorphic engineering, spike time dependent plasticity, stochastic computation, dendritic computation, unsupervised learning

#### **INTRODUCTION**

#### **PRIOR WORK**

Real neurons, the electrically excitable cells of the Eumetazoan, constitute an extremely diverse intractably complex community whose dynamic structures and functions defy all but the broadest generalizations (Herz et al., 2006; Llinas, 2008). In order to minimize this complexity, the field of Artificial Neural Networks (ANN) has traditionally modeled neurons as deterministic, centrally clocked elements which operate on real valued signals (Yegnanarayana, 1999). These signals represent neuronal rate coding where the spiking rate of a neuron encodes useful information and the adjustment of synaptic weights results in learning. This scheme, while mathematically amenable incurs a significant energy cost by discarding the rich temporal information available in the real signals used by neurons to communicate (Levy and Baxter, 1996; Laughlin, 2001; Van Rullen and Thorpe, 2001). In contrast, the highly optimized, low power, portable signal processing, and control system that is the brain readily uses temporal information embedded in the input signals and internal dynamics of its stochastic heterogeneous elements to process information (Xu et al., 2012).

More recently, the greater efficiency, higher performance, and biologically realistic dynamics of temporal coding neural networks has motivated the development of synaptic weight adaptation schemes that operate on temporally coding Spiking Neural Networks (SNN) (Jaeger, 2001; Maass et al., 2002; Izhikevich, 2006; Kasabov et al., 2013; Tapson et al., 2013; Gütig, 2014).

After proposition many of these models are followed soon by their implementation in neuromorphic hardware (Mitra et al., 2009; Indiveri et al., 2011; Beyeler et al., 2013; O'Connor et al., 2013; Chicca et al., 2014; Rahimi Azghadi et al., 2014). One of the problems faced by neuromorphic hardware engineers is the hardware inefficiency of many neural network algorithms. These algorithms are almost always initially designed for performance in a constraint free mathematical context with numerous all-to-all connected neurons and/or to satisfy some biological realism criteria, which create difficulties in hardware implementation.

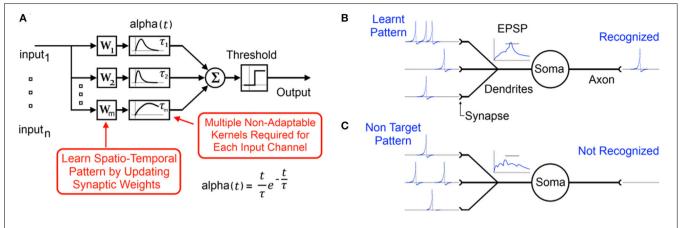

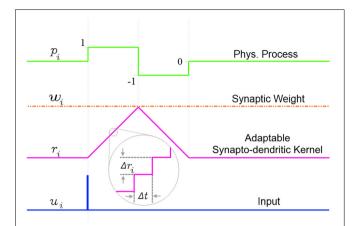

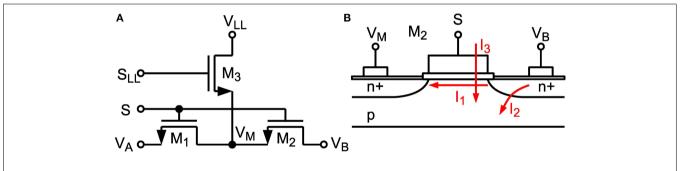

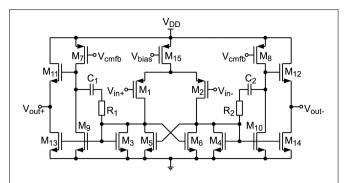

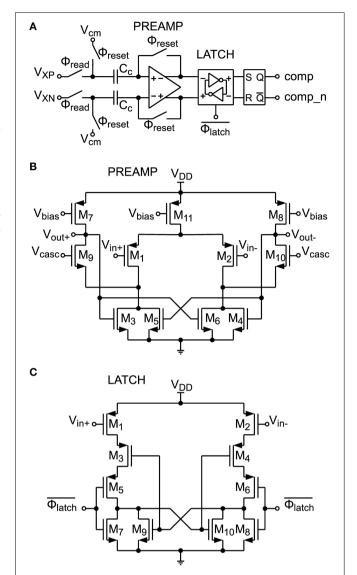

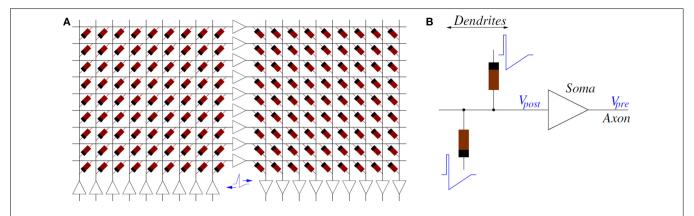

Additionally in order for such spiking systems to combine temporal coding and weight adaptation, multiple synapses consisting of synaptic transfer functions (or synaptic kernels) as well as synaptic weights must be realized for every input channel as shown in Figure 1. With the aim of being biologically plausible, exponentially decaying functions are typically chosen as the synaptic kernel, which is then multiplied by the synaptic weight. Such functions and weights are quite complex and difficult to implement in simple scalable analog and digital hardware with even the simplest schemes requiring at least one multiplication operation at every synapse. The difficulty of realizing multipliers at the synapse and the large number of synapses used in most algorithms has motivated moves toward more scalable digital synapses (Merolla et al., 2011; Seo et al., 2011; Arthur et al., 2012; Pfeil et al., 2012), novel memristor based solutions (Indiveri et al., 2013; Serrano-Gotarredona et al., 2013) and second order solutions such as sparse coding (Kim et al., 2014), time multiplexing,

**FIGURE 1 | (A)** Typical functional model of a spiking neuron with static synaptic transfer functions that provide memory of recent spikes. **(B)** Biological representation of the neuron showing the learnt input spike pattern,

the resultant Excitatory Post-Synaptic Potentiation (EPSP) and the output spike indicating pattern recognition. **(C)** Presentation of a non-target pattern results in an EPSP that does not cross the threshold producing no output spike.

and Address Event Representation (AER) (Zamarreno-Ramos et al., 2013) where only one or a few instances of the complex computational units are realized and these are utilized serially. Despite the success of these approaches such serial implementations can sometimes introduce associated bottlenecks, which can detract from the main strength of the neural network approach: its distributed nature (Misra and Saha, 2010).

Rather than implement complex synaptic weight adaptation, other neuromorphic SNN implementations have, in the last 3 years, focused exclusively on adjustment of explicit propagation delays along the neural signal path and coincidence detection of input spikes to encode memory (Scholze, 2011; Sheik et al., 2012, 2013; Dowrick et al., 2013; Hussain et al., 2014; Wang et al., 2014). This discarding of synaptic weights and kernels significantly simplifies implementation and improves scalability. The disadvantage is that explicit delay learning schemes can produce "sharp" systems with poor tolerance for the dynamically changing temporal variance they inevitably encounter in applications where neuronal systems are expected to excel: noisy, dynamic, and unpredictable environments.

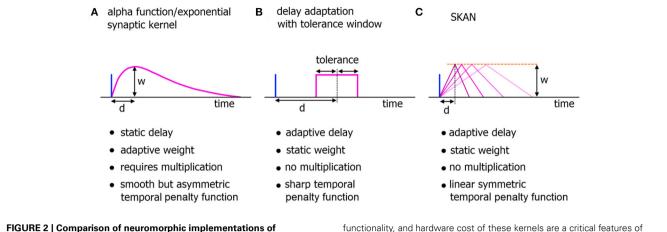

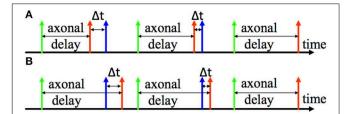

One of the features shared by all the preceding systems is that the kernels used for encoding temporal information are static as shown in Figure 2. However recent advances in neurophysiology have revealed that synapto-dendritic structures and their associated transfer functions are highly complex and adapt during learning in response to the statistical contexts of their stimulus environment (Losonczy et al., 2008; Yoshihara et al., 2009; Kasai et al., 2010a; Lee et al., 2012; Rochefort and Konnerth, 2012; Smith et al., 2013; Colgan and Yasuda, 2014). These discoveries are significant in the context of the computational power of even single biological neurons. Whereas in the traditional neuron model synapto-dendritic structures function as weights and cables connecting one soma to the next, the recent findings have demonstrated a wide range of signal integration and processing occurring along the signal path, which confers considerable computational power to single neurons (Spruston, 2008; Silver, 2010; Harnett et al., 2012; Papoutsi et al., 2014). These effects represent novel dynamics with as yet unexplored emergent computational properties, which may potentially solve currently

intractable problems in computational neuroscience (Bhatt et al., 2009; Shah et al., 2010). These dendritic adaptation effects have recently been modeled through large rule sets (Yu and Lee, 2003; Kasai et al., 2010b; Brunel et al., 2014) and in the neuromorphic field the use of dendrites for computation is beginning to be explored (Hsu et al., 2010; George et al., 2013; Ramakrishnan et al., 2013; Wang and Liu, 2013). However with biological realism as a major focus, many of the models carry significant extra complexity which can impede scalability.

#### **NEURONS AS FUNCTIONAL MODELS OF DISTRIBUTED PROCESSING**

In this paper the goal of performance in hardware motivates a change in focus from claims of accurate modeling of computation in biological neurons to exploiting the computational power of artificial but biologically inspired neurons. These are herein defined as a set of simple distributed informational processing units that communicate through binary valued pulses (spikes), receive inputs from multiple input channels (synapses and dendrites), and have a single output channel (axon).

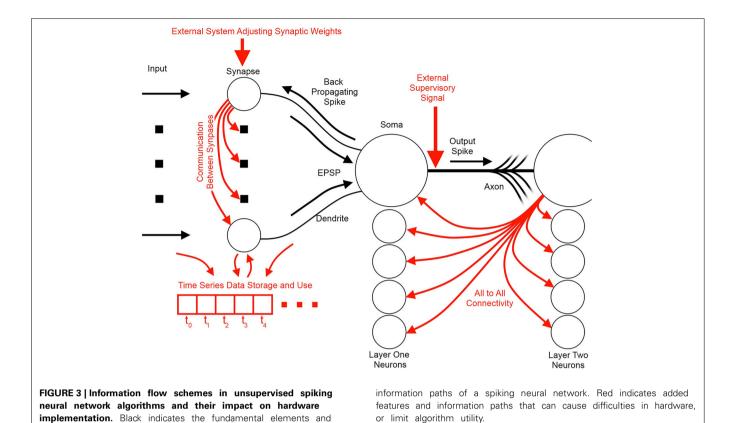

**Figure 3** illustrates the basic elements of SNN algorithms as well as some useful information flow and storage restrictions (red), which, if adhered to at the neuron design stage, prove helpful during the physical implementation stage. These restrictions include:

- 1. Self-contained: In a self-contained system, no external controlling system is required for the system to function. Examples of systems that are *not* self-contained include synapses that require adjustment via an external controller, or systems that assume an external supervisor in real world contexts where such a signal is unlikely to be available.

- Scalable connectivity: Systems that require all-to-all connectivity between the neurons or where the synapses or dendrites directly communicate their weights or potentials to each other are not hardware scalable or biologically possible. All-to-all connected neurons require a geometrically increasing number of connections, which is prohibitive both in hardware and in the brain (Topol et al., 2006; Bullmore and Sporns, 2012).

synapto-dendritic kernels. The characteristics of realized EPSP kernels are computationally important just prior to their being summed at the soma. These kernels represent the penalty function used to translate the temporal error in spatiotemporal spike patterns at the synapse to the membrane potential at the soma. Due to their large numbers, the complexity,

functionality, and hardware cost of these kernels are a critical features of neuromorphic spiking networks. (A) The biologically plausible alpha function with adaptive weights. The delay of the kernel is static. (B) A neuromorphic delay learning system with a temporal tolerance window. (C) The adaptable kernel of SKAN with adaptive delay when the kernel peak value/synaptic weight  $\boldsymbol{w}$  is kept constant as is the case in this work.

- 3. Storage of time series data: Systems whose processing units require large segments of their time series data to be stored and be accessible for later processing in the fashion of standard processors require a significant amount of on-site memory not possible in biological systems and would add significant complexity to neuromorphic hardware. Furthermore, such systems overlap the domain of distributed processors such as GPUs and fall outside the neuromorphic scope.

- 4. Multiplication: Multipliers are typically inefficient to implement in hardware and are limited in standard digital solutions such as Field Programmable Gate Arrays (FPGAs) and Digital Signal Processors (DSPs). Their computational inefficiency and their limited number available on a hardware platform result in neural networks implemented with timemultiplexing. This, in turn, limits the size and the applications where this hardware is viable (Zhu and Sutton, 2003; Pfeil et al., 2012).

#### **MATERIALS AND METHODS**

The elements of Synapto-dendritic Kernel Adapting Neuron (SKAN) and its learning rule are defined in the first part of this section. In the second part, the dynamical behaviors of SKAN are described.

#### **SKAN BUILDING BLOCKS**

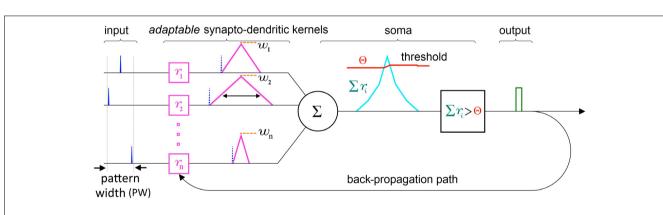

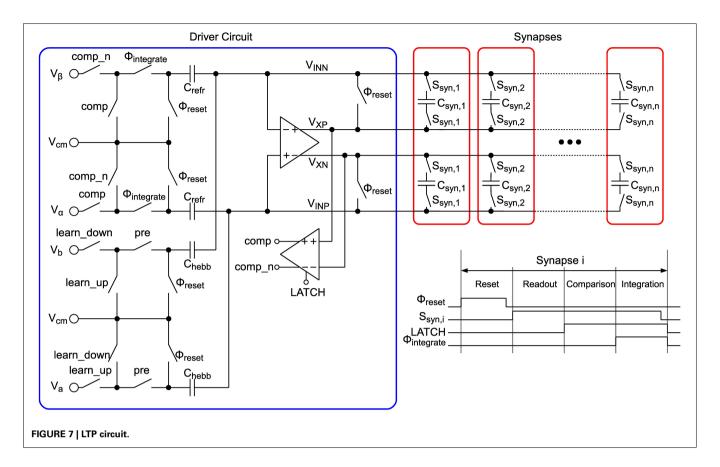

At the single neuron level, SKAN consists of a combined synaptodendritic kernel adaptation and a homeostatic soma with an adapting threshold as shown in **Figure 4**.

#### Synapse/dendrite

An incoming input spike initiates a simplified synapto-dendritic kernel at each input channel i. This kernel is controlled by a physiological process,  $p_i$ , and for simplicity is modeled as a ramp up and a ramp down sequence generated via an accumulator  $r_i$  with step size  $\Delta r_i$ . An input spike triggers  $p_i$ , starting the first phase where the accumulator ramps up at each time step  $\Delta t$  by  $\Delta r_i$

until it reaches a maximum value  $w_i$  which represents the synaptic weight, and which is kept constant throughout this paper to simplify the algorithm. After  $r_i$  reaches  $w_i$ , the process switches from the ramp up phase,  $p_i = 1$ , to a ramp down phase,  $p_i = -1$ , which causes the accumulator to count down at each time step toward zero with the same step size  $\Delta r_i$ , until it reaches zero, turning off the physiological process,  $p_i = 0$ . It will stay in this state until a new incoming spike re-initiates the sequence. This simple conceptual sequence, which is analogous to a dendritically filtered neuronal EPSP, is illustrated in **Figure 5**.

The state of the ramp up ramp down flag sequence is described by Equation 1:

$$p_{i}(t) = \begin{cases} 1 & \text{if } (u_{i}(t) = 1 \land p_{i}(t-1) = 0) \\ & \lor (p_{i}(t-1) = 1 \land r_{i}(t-1) < w_{i}) \\ -1 & \text{if } (p_{i}(t-1) = 1 \land r_{i}(t-1) \ge w_{i}) \\ & \lor (p_{i}(t-1) = -1 \land r_{i}(t-1) > 0) \\ 0 & \text{else} \end{cases}$$

(1)

The *w* parameter in SKAN has similarities to the weight by which a synaptic kernel is multiplied in standard synaptic STDP neuron models and neuromorphic circuits, but with the advantage of not requiring any multipliers, which are otherwise required at every synapse in hardware implementations. The adjustment of *w* in SKAN, via standard synaptic STDP schemes would allow synaptic prioritization and/or the closing off of inactive or noisy channels. The combined effects of dendritic structure and synaptic weight plasticity has only recently begun to be explored, but early evidence points to significant computational power of such a combined system (Sjöström et al., 2008). In this paper, however, in order to clearly demonstrate the stand-alone capabilities of SKAN's synapto-dendritic kernel adaptation mechanism, the synaptic weight parameter of *w* is held constant and is identical for all synapses.

FIGURE 4 | Schematic of the elements and information paths in a SKAN neuron. The input spikes (blue) trigger adaptable synapto-dendritic kernels (magenta) which are summed to form the neuron's somatic membrane potential (cyan). This is then compared to an adaptive somatic threshold (red) which, if exceeded, results in an output pulse (green). The

output pulse also feeds back to adapt the kernels. Note that in this paper the synaptic weights (orange) are held constant and equal for all synapses. Also note that the back propagating signal does not travel beyond the synapto-dendritic structures of the neuron to previous neural layers.

#### Soma

At the soma the synapto-dendritic kernels are summed together. This summed term is analogous to the membrane potential of a biological neuron. Along with the membrane potential the soma uses a dynamic threshold voltage parameter  $\Theta(t)$  and as long as the membrane potential exceeds threshold, the soma spikes, setting the binary s(t) from 0 to 1 as described in Equation 2:

$$s(t) = \begin{cases} 1 & \text{if } \sum_{i} r_i(t) > \Theta(t-1) \\ 0 & \text{else} \end{cases}$$

(2)

SKAN differs from most previous spiking neuron models in not resetting the membrane potential after spiking (see Denève, 2008; Tapson et al., 2013 for exceptions). This permits wide pulse widths at the neuron output s(t). While such wide pulses do

#### FIGURE 5 | The simplified adaptable synapto-dendritic kernel of SKAN.

An input spike (blue) triggers the kernel's ramp up ramp down sequence. The input spike sets a flag  $p_i$  representing a physical process to one (green). The flag causes an accumulator (magenta) to count up from zero by  $\Delta r_i$  at each time step until it reaches  $w_i$  (constant orange dotted line), after which the flag is set to negative one, which causes the accumulator to count back down to zero, at which point the flag returns to zero completing the sequence. The value of the accumulator represents the synapto-dendritic kernel, i.e., the post-synaptic potential, which travels to the soma and is summed with other kernels to produce the somatic membrane potential.

not resemble the canonical form of the single spike, they are analogous to concentrated spike bursts and play a significant part in the functioning of SKAN.

#### FEEDBACK MECHANISMS/LEARNING RULES

#### Synapto-dendritic kernel slope adaption

One of the central elements of SKAN is the feedback effect of the output pulse s(t) on each of the synapto-dendritic kernels. Here s(t) is analogous to the back propagating spike signal in biological neurons which travels back up the dendrites toward the synapses and is responsible for synaptic STDP.

The logic of the kernel adaptation rule is simple; if a particular dendrite is in the ramp up phase  $p_i=1$  and the back propagation signal s(t) is active, the soma has spiked and this particular kernel is late to reach its peak, meaning that the other kernels have cooperatively forced the membrane potential above the threshold while this kernel has yet to reach its maximum value  $w_i$ . In response, the ramp's step size  $\Delta r_i$  is increased by some small positive value ddr for as long as the output pulse is high [s(t)=1] and the kernel is in the ramp up phase. Similarly if a kernel is in the ramp down phase  $p_i=-1$  when the back propagation signal is high, then the kernel peaked too early, having reached  $w_i$  and ramping down before the neuron's other kernels. In this case the ramp step size  $\Delta r_i$  is decreased by ddr. Equation 3 describes this simple kernel adaptation rule:

$$\begin{bmatrix} r_i(t) \\ \Delta r_i(t) \end{bmatrix} = \begin{bmatrix} r_i(t-1) \\ \Delta r_i(t-1) \end{bmatrix} + p_i(t-1) \begin{bmatrix} \Delta r_i(t-1) \\ ddr \times s(t-1) \end{bmatrix}$$

(3)

The use of indirect evidence about the dynamic state of other dendrites in the form of the back propagating spike is a central feature

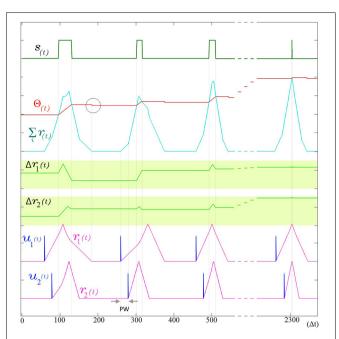

FIGURE 6 | The adaptation of SKAN. The kernels and the threshold of SKAN adapt in response to repeated spatio-temporal pattern presentations. For visual clarity the pattern only consists of the Inter-Spike Interval (ISI) across two input channels  $u_i(t)$  such that the pattern width (PW) is equivalent to the ISI. By the third presentation of the pattern the kernels have captured the ISI information. With each subsequent presentation the threshold  $\Theta(t)$  increases making the neuron more selective as the kernel step sizes  $\Delta r_i(t)$  increase making the kernels narrower. As a result each pattern presentation increases the neuron's confidence about the underlying process producing the ISI's, narrowing the neuron's receptive field around the target ISI and producing a smaller output pulse s(t) until, by the 11th presentation ( $t=2300~\Delta t$ ), the  $\Theta_{\textit{rise}}$  during the output spike and  $\Theta_{\it fall}$  balance each other such that the  $\Theta_{\it before} \approx \Theta_{\it after}$ . The soma output spike s(t) is now a finely tuned unit delta pulse which indicates high certainty. When the membrane potential returns to zero, the neuron's threshold falls as indicated by the gray circle.

in the operation of SKAN and enables the synchronization of all the neuron's dendritic kernel peaks as shown in **Figure 6**.

#### Threshold adaptation

The threshold of SKAN is adaptive and changes under two conditions: when the neuron outputs a spike and when the membrane potential returns to zero.

At every time step during an output pulse s(t) = 1 the threshold increases by  $\Theta_{rise}$ . This increase in the threshold is analogous to the frequency adaptation effect seen in neurons, which creates a feedback loop reducing the ability of the neuron to spike. Similarly in SKAN, the higher threshold reduces the likelihood and duration of an output pulse. This effect is shown in **Figure 6** and described in the first line of Equation 4.

$$\begin{split} \Theta(t) &= \\ \begin{cases} \Theta(t-1) + \Theta_{rise} & \text{if } \sum_{i} r_i(t) > \Theta(t-1) \\ \Theta(t-1) - \Theta_{fall} & \text{if } \sum_{i} r_i(t) = 0 \land \sum_{i} r_i(t-1) > 0 \end{cases} (4) \\ \Theta(t-1) & \text{else} \end{cases}$$

The post spike decrease in threshold  $\Theta_{fall}$  operates in opposition to the  $\Theta_{rise}$  term. The returning of the membrane potential  $\Sigma r_i(t)$  to zero causes a decrease in the threshold by  $\Theta_{fall}$  as described by the second line of Equation 4 and shown in **Figure 6**. The counter balancing effect produced by the  $\Theta_{fall}$  and  $\Theta_{rise}$  in SKAN is a highly simplified version of the complex mechanisms underlying spike-threshold and frequency adaption in biological neurons (Fontaine et al., 2014; Lee et al., 2014), where excited neurons eventually reach an equilibrium state through homeostatic processes such that the average spike frequency of neurons with a constant input tends asymptotically toward a non-zero value as  $t \to \infty$ . This simple rule set describes all the elements of a single SKAN.

#### SINGLE SKAN DYNAMICS

In this section the dynamics emerging from SKAN's rule are discussed for the single neuron case.

#### Observing the first spike in a spike train or burst

As described in the first line of Equation 1 the ramp up phase of the kernel at channel i is only initiated if a spike arrives at the channel  $(u_i = 1)$  while and the kernel is inactive  $(p_i = 0)$ . As a result while the ith kernel is active no further input spikes are observed. This has the effect that for each input channel the neuron trains on the first spike of a spike train or burst. For the case where the spike train or burst is of shorter duration than the total duration of the kernel, the behavior of the neuron is identical one where the burst is replaced by a single input spike arriving at the start of the burst. The effect of more general Poisson noise spikes is described later in this section.

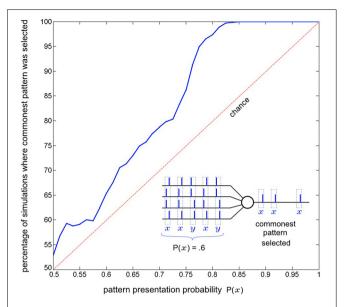

#### Selecting to learn the commonest spatio-temporal patterns

As a single neuron, SKAN has previously been shown to select and learn the most common spatio-pattern presented in a random sequence containing multiple patterns (Sofatzis et al., 2014a). This effect has been demonstrated in the context of visual processing where hand gestures were transformed to spatio-temporal patterns via a neuronal transform operation (Afshar et al., 2013) and processed by SKAN (Sofatzis et al., 2014b). **Figure 7** shows the performance of a four input neuron as a function of spatio-temporal pattern probability. The graph shows that the neuron's selection of commonest pattern is significantly above chance such that for sequences with  $P(\mathbf{x}) > 0.85$  only the more common pattern will selected.

### SKAN response time improves with adaptation without information loss

In addition to the kernel adaptation and increasing threshold effect, the response time of SKAN, i.e., the time from the last arriving input spike in a pattern to the neuron's output spike, decreases with every pattern presentation. This effect, shown in **Figure 8**, is absent in the standard STDP schemes where improved response times comes at the cost of information loss. In STDP schemes the earliest spikes in a spatio-temporal pattern tend to be highly weighted while the later spike lose weight and have little effect on recognition (Masquelier et al., 2009). This behavior can be seen as advantageous if an assumption is made that the later

FIGURE 7 | Commonest pattern selection as a function of pattern presentation probability. The inset illustrates one simulation a 5 pattern long sequence where each pattern is sampled from two randomly initialized spatio-temporal patterns x and y, with probability P(x) = 0.6. In this particular simulation pattern x was selected by the neuron. The plot shows data resulting from the same experiment but with 1000 simulations of 300 pattern long sequences for each probability P(x) = 0.5 to 1. The graph shows that the likelihood of a pattern being selected rises with increasing presentation probability. For each simulation the output of the neuron for the second half of the sequence (150-300th pattern) was recorded and it was determined whether pattern x or pattern y had been selected. Also tested was whether both, or neither pattern was selected by the neuron at some point during the sequence (i.e., the neuron spiked at least once for both of the patterns or failed to spike for a pattern it had selected during the sequence). In the more than seven million pattern presentations  $(1000 \times 150 \times 51)$  neither of these occurred.

spikes in carry less information however in this is an assumption that cannot be made in general. In contrast SKAN's adaptable kernels reduce output spike latency with adaptation while still enabling every spike to affect the output. This effect proves critical in the context of a multi-SKAN competitive network, where the best-adapted neuron is also always the fastest neuron to spike.

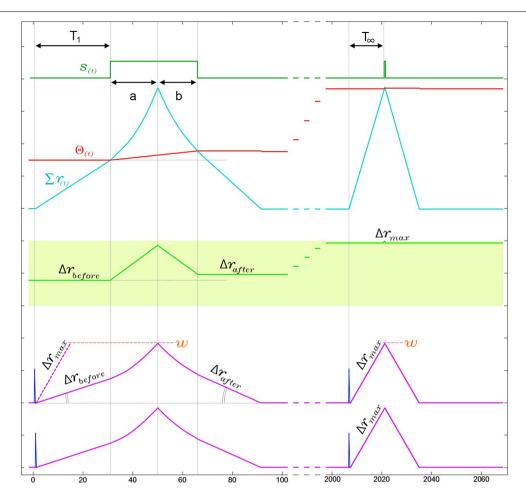

As shown in **Figure 8**, the combination of the kernel and threshold adaptation rules of SKAN increases  $\Delta r$  and decreases the response time between the last arriving input spike and the rising edge of the output spike with each presentation. If this increase is left unchecked  $\Delta r$  will increase until it equals w at which point the kernels take the shape of a single pulse such that  $T_{\infty} = 1\Delta t$ . To prevent this  $\Delta r$  must saturate at  $\Delta r_{max}$  as shown in **Figure 8** with  $\Delta r_{max}$  limited by Equation 5. This restriction ensures that the kernel of the first spike in an input pattern cannot return to zero before the last spike in the pattern arrives enabling all kernels to converge due to feedback from the same output signal.

$$\Delta r_{max} < w/PW$$

(5)

where PW is the maximal pattern width of the target pattern.

FIGURE 8 | Narrowing of kernels leads to improved response time during neuronal adaptation in a two input neuron. For visual clarity the neuron is presented with an ISI =  $0\Delta t$  pattern and the two kernels start with identical initial slopes  $[\Delta r_1(0) = \Delta r_2(0) = \Delta r_{before}]$ . In the region under the output pulse, r(t) is the second integral of the constant ddr and therefore follows time symmetric parabolic paths (a) and (b) as it rises and falls. However due to the threshold rise which also occurs during the output pulse, the output pulse is not symmetric around the

r(t) peak, such that the parabolic ramp down phase (b) is shorter than the parabolic ramp up phase (a). As a result of this asymmetry  $\Delta r_{after}$  is larger than  $\Delta r_{before}$ . This effect increases the kernel's slope  $\Delta r$  with each pattern presentation, narrowing the kernels until  $\Delta r$  reaches  $\Delta r_{max}$ . As a result of this narrowing, the response time of the neuron from last arriving input spike to the rising edge of the output, which is  $T_1$  in the first presentation, improves until it reaches its minimal possible value  $T_{\infty} \approx w/\Delta r_{max}$ .

# Evolution of the temporal receptive field in SKAN approximates statistical inference

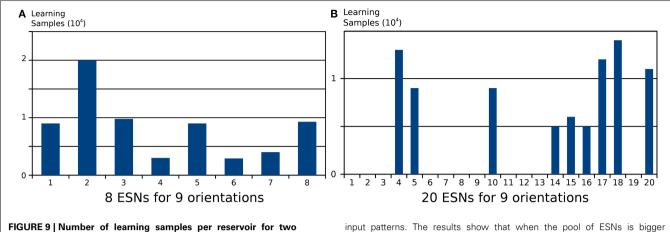

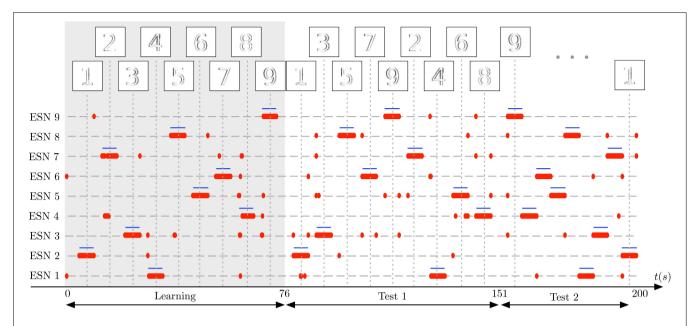

Recent work has demonstrated the connection between synaptic weight adaptation and approximate probabilistic inference in the context of rate coding and spiking networks (Bastos et al., 2012; Boerlin et al., 2013; Pouget et al., 2013; Corneil et al., 2014; Kappel et al., 2014; Kuhlmann et al., 2014; Paulin and van Schaik, 2014; Tully et al., 2014), where typically the state of binary hidden variables are inferred from noisy observations using a large number of neurons. In this section we show that synapto-dendritic kernel adaptation enables a single neuron to make statistical inferences not about binary hidden variables but about hidden ISI generating processes. **Figure 9** illustrates the evolution of the temporal receptive field of a neuron with two inputs as the neuron attempts to learn the statistics of an underlying process that produces ISIs with linearly increasingly temporal jitter. The receptive field of the

www.frontiersin.org

neuron describes the amount by which the membrane potential  $\Sigma r_i(t)$  exceeds the threshold  $\Theta(t)$  as a function of the input spike pattern times of  $u_i(t)$ . For the simple two input case illustrated, the receptive field is a scalar function of the one-dimensional ISI. In order to calculate the receptive field, following each pattern presentation the neuron's new parameters  $(\Delta r_i \text{ and } \Theta)$  were saved and the neuron was simulated repeatedly using these saved parameters for every possible ISI given the maximum pattern width PW. For each simulation the summation in Equation 6 was calculated at the end of the simulation resulting in the receptive fields shown in **Figure 9**.

$$RF_{i=2}(\tau) = \sum_{t} \left( \sum_{i} r_{i}(\tau, t) - \Theta(\tau, t) \right) \times s(\tau, t)$$

(6)

where  $\tau$  is the ISI being simulated.

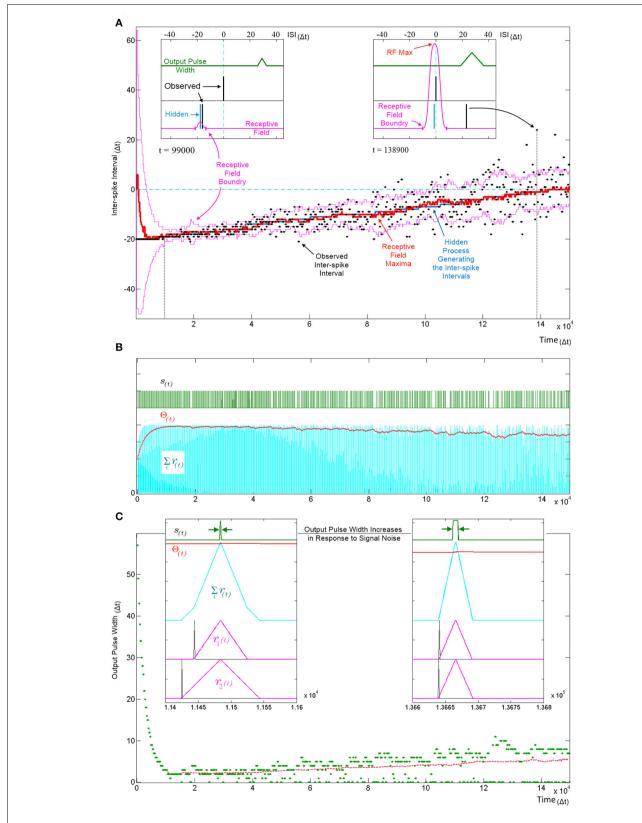

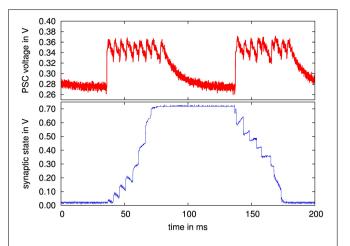

FIGURE 9 | Tracking a hidden ISI producing process and its variance. All three panels (A-C) show different aspects of the same simulation where a single SKAN learns statistics of a dynamic ISI across two input channels. (A) A hidden process (blue) moves from  $ISI = -20 \Delta t$  to  $ISI = 0 \Delta t$ . The process

begins with no temporal jitter noise, such that the observed ISI's (black dots) equal the hidden process ( $\sigma=0\Delta \it{t}$ ) and the blue hidden process is covered by the observed black dots. At t = 0, the sum of the neuron's randomly (Continued)

#### FIGURE 9 | Continued

initialized kernels peak at ISI = 6  $\Delta t$ . As the kernels adapt and capture the ISI information, the receptive field maximum (red line) converges on to the observed ISIs. This causes the threshold to rise shrinking the receptive field to a minimum size (left inset  $t=9.9~\mathrm{k}\Delta t$ ). At this stage receptive field boundaries (pink lines) lie very close on either side of the hidden process' mean value. As the simulation continues the noise in the ISI producing process is deliberately increased linearly with time. The neuron continues to follow the process but with every spike that doesn't land on the receptive field maximum the threshold falls slightly which increases the receptive field size and increases the neuron's receptivity to ever more unlikely observations (right inset  $t=138.9~\mathrm{k}\Delta t$ ). (B) Variables and behavior of the neuron throughout the simulation: after a rapid initial increase the threshold  $\Theta(t)$  settles near the peak of the membrane potential  $\Sigma r_i(t)$ . As the noise increases linearly the threshold begins to

fall gradually. Missing output spikes in the s(t) spike train correspond to input spikes that have landed outside the receptive field boundaries. **(C)** The output pulse width (green = observed, red = running average) increases with increasing signal noise. As with the receptive field size, the output pulse width is initially large. As more patterns are observed, the threshold rises and settles just below the peak of the membrane potential and the pulse width reaches a minimum width of 1–2  $\Delta t$ . At this low noise level ( $\sigma \approx 0.5 \Delta t$ ) there are no missing outputs, such that all pulse widths are above zero. As the noise increases, more ISIs land away from the receptive field maximum and some fall completely outside the receptive field, decreasing the threshold, which results in wider output pulse width whenever observed ISI's do land near the receptive field maximum. The dashed magenta line tracks the mean spike width, which also increases with noise. This illustrates that the mean output pulse width of SKAN is a reliable correlate of input noise level.

The ISI at which the receptive field expression above is at its maximum (*RF* Max) indicates the ISI for which the neuron is most receptive and may be interpreted as the ISI expected by the neuron. Similarly the ISI boundary where the receptive field expression goes to zero is the limit to the range of ISI's expected by the neuron. An ISI falling outside the receptive field boundaries results in no spike and no adaptation but simply reduces the neuron's confidence and can be viewed as outlier.

Figure 9A shows SKAN's receptive fields tracking the statistics of a moving ISI generating process with dynamic noise levels with a high level of accuracy such that the blue line indicating the hidden process is barely visible from under the red line marking the receptive field maximum. Figure 9C shows the neuron transmitting wider output or bursts with increasing noise. In addition, increasing ISI noise causes a growing gap between the envelope of the pulse widths and the running average of the pulse widths. This increasing gap is critical to the operation of the neuron, as it is caused by missed pattern presentations, i.e., patterns that produce no output pulse because of the presented noisy pattern being too dissimilar to the one the neuron has learnt and expects. The effect of a missed pattern is a fall in the neuron's threshold by  $\Theta_{fall}$ . When presented with noiseless patterns this fall would be balanced almost exactly by the threshold rise due to the  $\Theta_{rise}$ term in Equation 4 during the output pulse. However, without the output spike there is a net drop in threshold. Yet this lower threshold also makes the neuron more receptive to noisier patterns creating a feedback system with two opposing tendencies which:

- Progressively narrows kernels around the observed input pattern while shrinking the neuron's receptive field by raising the threshold.

- 2. Expands the receptive field in response to missed patterns by reducing the threshold while allowing the kernels to learn by incorporating ever less likely patterns.

The balance between these two opposing tendencies is determined by the ratio  $\Theta_{rise}$ :  $\Theta_{fall}$ , which controls how responsive the neuron is to changing statistics. With a stable noise level SKAN's dynamics always move toward an equilibrium state where the neuron's tendency to contract its receptive field is precisely balanced by the number of noisy patterns not falling at the

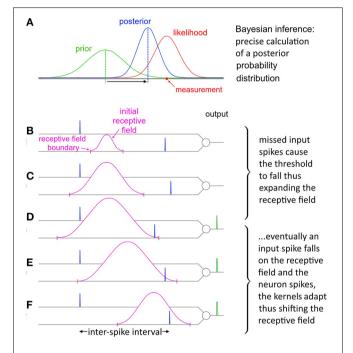

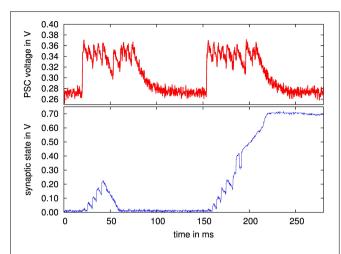

#### FIGURE 10 | Evolution of SKAN's receptive field in response to input.

(A) Total resultant change in SKAN's receptive field after multiple pattern presentations. (B) SKAN with a small initial receptive field which does not match the ISI distribution. The input spike lands outside the receptive field boundaries. (C) As more ISI's fall outside the small receptive field the threshold falls and the receptive field expands, but without shifting the position of its maximum value. (D) An ISI just falls on to the greatly expanded receptive field producing an output spike. (E) The output spike causes the SKAN kernels to adapt shifting the receptive field toward the true position of the underlying process. (F) As more and more ISI's fall closer to the receptive field maximum wider output pulses are produced which adapt the kernels faster shifting the receptive field more rapidly while the resultant rise in the threshold contracts the receptive field. With enough observations the receptive field would eventually become centered on the input ISI distribution with the receptive field boundaries tracking the ISI's distribution.

receptive field maximum. This heuristic strategy results in the receptive field's maximum and extent tracking the expected value of the input ISI's and their variance respectively as shown in Figure 10.

## LEARNING IN THE PRESENCE OF POISSON SPIKE NOISE AND MISSING TARGET SPIKES

In addition to robustness to temporal jitter in the put pattern an important feature of neural systems is their performance in the presence of Poisson spike noise. Recent work has highlighted that unlike most engineered systems where noise is assumed to degrade performance, biological neural networks can often utilize such noise as a resource (McDonnell and Ward, 2011; Hunsberger et al., 2014; Maass, 2014). In

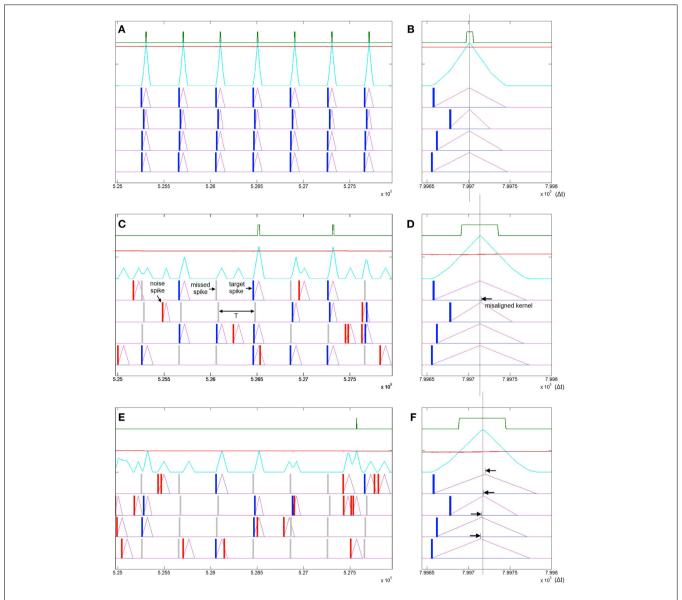

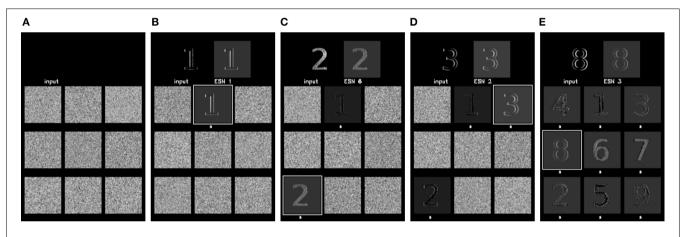

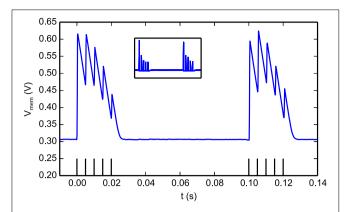

the neuromorphic context the performance of neural network architectures in the presence of noise is well documented (Hamilton and Tapson, 2011; Hamilton et al., 2014; Marr and Hasler, 2014). To test SKAN's potential performance in stochastic real world environments, the combined effects of extra noise spikes as well as missing target spikes needs to be tested. **Figure 11** illustrates how different signal to noise ratios can affect SKAN's ability to learn an embedded spatio-temporal spike pattern.

FIGURE 11 | Learning spatio-temporal spike patterns in the presence of both Poisson spike noise and missing target spikes. Panel (A) shows the presentation of seven patterns in the middle of a simulation sequence with a noiseless environment. The kernels are highly adapted ( $\Delta r_2 = \Delta r_{max}$ ), the threshold is high and the output spikes are narrow indicating high certainty. Panel (B) shows the result of a final noiseless test pattern at the end of the simulation showing in detail that the kernels resulting from the test pattern peak at the same time. Panel (C) shows the same interval of the same

simulation as panel **(A)** but with a 1:1 signal to noise ratio where the probability of a target spike being deleted is half or P(signal) = 0.5 and the Poisson rate is also half such that P(noise) = 0.5/T. Panel **(D)** shows the result of a noiseless test pattern presentation at the end of the simulation. The increased level of noise has resulted in an incorrect ramp step  $(\Delta r_2)$  such that the  $r_2$  kernel peaks slightly late (black arrow). Panel **(E)** shows a simulation with a 1:2 signal to noise ratio. Panel **(F)** shows that the high noise level has resulted in slight misalignment of all four kernels.

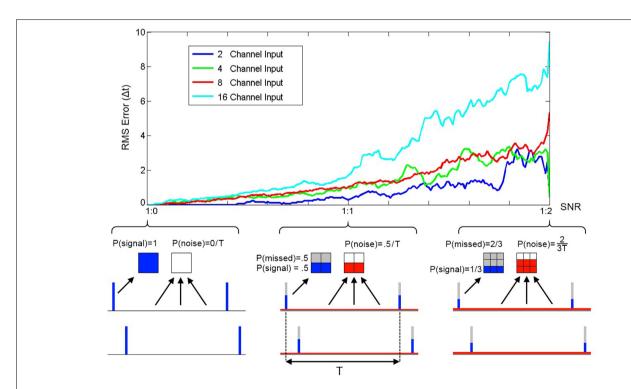

To quantify the performance of SKAN in the presence of Poisson noise and missing target spikes a series of simulations each comprising of 2000 pattern presentations were performed. At the end of each simulation the RMS error between the neuron's receptive field maxima and the random target pattern was measured and is shown in Figure 12.

#### **MULTI-SKAN CLASSIFIER**

In order to extend a single learning neuron to a classifier network it is important that different neurons learn different patterns. Ideally a neuron in a layer should not be in anyway affected by the presentation of a pattern that another neuron in the same layer has already learnt or is better placed to learn.

As outlined in Equation 3, SKAN adapts its kernels only during an output pulse. This rule is particularly conducive to competitive learning such that the simple disabling of the neuron's spiking ability disables all learning. Whereas previously proposed algorithms utilize multi neuron Winner-Take-All layers with real valued rate based inhibitory signals to prevent correlated spiking and maximize the network learning capacity (Gupta and Long, 2009; Nessler et al., 2013), in a SKAN network a simple global inhibitory OR gate serves the same function. The reason a simple binary signal can be used here is that in a SKAN network the best-placed neuron for any pattern will be the fastest neuron to spike. This allows a layer of neurons with shared inputs to learn to recognize mutually exclusive spatio-temporal patterns. To this end, Equation 2, describing the neuron's output, is replaced by Equation 7 (underlined terms added). The addition of a global decaying inhibitory signal as described in Equation 8, act on all neurons to disable any rising edge at the output. This means that neuron n can only *initiate* an output spike  $s_n$  if no other neuron has recently spiked, i.e., the inhibitory signal is inactive [inh(t-1)=0] and it can only continue spiking if it was already spiking in the last time step  $[s_n(t-1) = 0]$ .

$$s_{n}(t) = \begin{cases} 1 & \text{if } \sum_{i} r_{n,i}(t) > \Theta_{n}(t-1) \\ & \wedge (inh(t-1) = 0 \vee s_{n}(t-1) = 1) \\ 0 & \text{else} \end{cases}$$

(7)

$$inh(t) = \begin{cases} inh_{max} & \text{if } \bigcup_{n} s_{n}(t) = 1 \\ inh(t-1) - inh_{decay} & \text{if } inh(t-1) > 0 \\ 0 & \text{else} \end{cases}$$

$$inh(t) = \begin{cases} inh_{max} & \text{if } \bigcup_{n} s_n(t) = 1\\ inh(t-1) - inh_{decay} & \text{if } inh(t-1) > 0\\ 0 & \text{else} \end{cases}$$

(8)

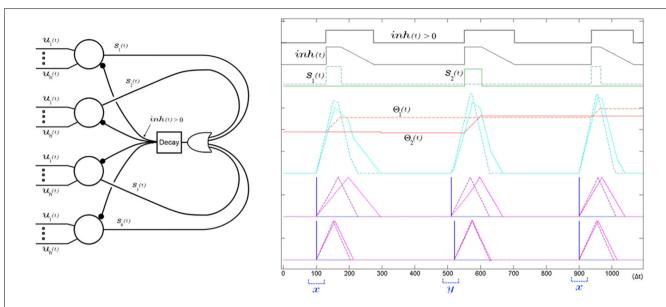

As shown in Figure 13 and described in Equation 8, the inhibitory signal is realized via an OR operation on the output of all neurons, and a decaying behavior which keeps the inhibitory signal active for a period of time after a neuron has spiked to prevent spiking by other neurons. After the output spike ends, this feedback loop decays from inhmax by inhdecay at each time step until reaching zero at which point the global inhibitory signal turns off allowing any neuron to spike. As shown in Figure 13 the decay only begins at the end of the pulse making the inhibitory signal operate as

FIGURE 12 | RMS error between receptive field maxima and target spike patterns as a function of spike signal to noise ratio. The three bottom panels show the spike probability distributions at three points along the SNR axis. The signal spikes (blue), missed spikes (gray), and noise spikes (red) are illustrated for the three cases of 1:0, 1:1, and 1:2 signal to noise ratios. The mean spike rate was maintained at 1 spike

per channel per time period between pattern presentations T. At the completion of a simulation with one thousand pattern presentations the RMS error between the resulting receptive field maxima and the target spatio-temporal pattern was calculated. As the plot illustrates the error increases with noise and simulations of neurons with more input channels resulted in higher error.

FIGURE 13 | A single global decaying inhibitory signal suffices to push apart the neurons' receptive fields and decorrelate the spiking of the SKAN network. Left panel shows the network diagram of four neurons with an inhibitory signal. The decay feedback loop extends the duration of the inhibitory signal beyond the initial triggering spike via the inh(t) signal using a counter and a comparator in the decay block. The right panel shows the simulation results from a two input two neuron network learning to classify two ISI's x and y. The sum of the randomly initialized kernels of neuron one (dashed) happen to peak earlier than neuron two (solid) so that neuron one fires first in response to the first pattern (x with ISI = 0  $\Delta t$ ). During this first output pulse neuron one's threshold rises sharply reducing its receptivity, while its kernel step sizes

adapt toward each other such that  $\Delta r_{1,1} \approx \Delta r_{1,2}$ . Meanwhile the inhibitory signal blocks neuron two from spiking when its kernel sum exceeds its threshold only a few time steps after neuron one, which means the neuron is prevented from adapting to pattern x. At the second pattern presentation pattern y is shown (ISI = 10  $\Delta t$ ). For this pattern the sum of the kernels of the second neuron, still unchanged from their random initialization, reach that neuron's threshold slightly earlier than neuron one and so neuron two spikes and begins adapting to pattern y. A subsequent presentation of pattern x again triggers neuron one and the kernels of the two neurons increasingly fine tune to their respectively chosen pattern with each presentation as their thresholds rises reducing their receptivity to other patterns.

a global peak detector which stays at  $inh_{max}$  for the duration of the pulse, ensuring that the inhibitory signal robustly suppresses spiking activity for a wide range of potential output pulse widths.

As with the single neuron output rule, the single neuron threshold adaptation rule of Equation 4 can be modified to Equation 9 (underlined terms added) to utilize the global inhibitory signal for the multi-neuron case. This modification prevents a neuron's threshold being affected by the presentation of patterns that another neuron is better adapted to. The addition of the underlined terms in the first line of Equation 9 means that a neuron's threshold can only rise when its membrane potential exceeds its threshold and the inhibitory signal is not already active, or if the neuron itself spiked in the previous time step. The fall in the threshold is similarly conditioned on the neuron having spiked *before* the global inhibitory signal was activated, such that only the very best adapted neuron, i.e., the one that generated the inhibitory signal in the first place, adapts its threshold.

$$\begin{split} \Theta_n(t) &= \\ \begin{cases} \Theta(t-1) + \Theta_{rise} & \text{if } \sum_i r_i(t) > \Theta(t-1) \\ \Theta(t-1) - \Theta_{fall} & \frac{\wedge (inh(t-1) = 0 \vee s_n(t-1) = 1)}{\text{if } \left(\sum_i r_i(t) = 0 \wedge \sum_i r_i(t-1) > 0 \right. \\ & \frac{\wedge inh(t-1) = 0)}{\vee (s(t) = 0 \wedge s(t-1) = 1)} \\ \Theta(t-1) & \text{else} \end{cases} \tag{9} \end{split}$$

Such a global inhibitory signal has been utilized in LIF neurons (Afshar et al., 2012; Tapson and van Schaik, 2012) and synaptic weight STDP neurons as a means of decorrelating neuronal firing patterns (Masquelier et al., 2009; Habenschuss et al., 2013). Here, however, its use is subtly different from both. Although in LIF and synaptic STDP architectures and in SKAN a global inhibitory signal results in the decorrelation of output spikes, in the purely synaptic weight adapting schemes the neuron's response time remains static and does not improve with adaptation and in the LIF networks (Afshar et al., 2012; Tapson and van Schaik, 2012) there is no lasting adaptation at all. SKAN's improved response time due to kernel adaptation and the global inhibitory signal realize a positive feedback mechanism absent in previous models. In a SKAN network a neuron's small initial advantage for a pattern results in a slightly earlier output spike. This output spike globally inhibits all other neurons, which in turn results in exclusive adaptation to the pattern by the first spiking neuron. This further improves that neuron's response time for the pattern and increases the likelihood of the neuron being the first to spike due to a subsequent presentation of the same pattern, even in the presence of temporal jitter. Thus, the adaptation of SKAN's kernels and thresholds, together with the global inhibitory network, mean that the neuron whose initial state is closest to the presented pattern will be the first to respond and prevent all other neurons adapting to this pattern. This effectively "hides" the pattern from the other neurons and allows unsupervised spike pattern

classification by the network as whole as demonstrated in the proceeding Results Sections.

There are two important constraints adhered to by the preceding modification of the SKAN rules. The first constraint is that the required connectivity does not increase combinatorially with the number of neurons as described in Equation 10 since the only feedback path is from the single global inhibitory signal.

total connections = (number of input channel

$$+ 2$$

)

× number of neurons (10)

The second constraint is that no complex central controller is required for arbitration between the neurons. In competitive neural network schemes where a neuron's fitness is expressed as a real value from each neuron to a Winner-Take-All network, multiple bits (connections in hardware) are required to transport this information. Alternatively rate based systems encode such real valued signal over time in their spike rate which are then utilized by a corresponding rate based Winner-Take-All system. But in SKAN these requirements are reduced. Since a neuron's latencies correlates with its adaptation to a target pattern, the neurons do not need to report a real value but only a single bit. This mode of operation can be interpreted as either a connectivity saving or as a speed saving with respect to alternative multi-bit or rate based systems respectively. Furthermore, because of the robustness of the system, checking for, or prevention of, simultaneous output spikes is not necessary. Random initial heterogeneities in the neurons' parameters and/or noise in their signals is enough to eliminate the need for central control by pushing the neurons away from input space saddle points toward their stable non-overlapping receptive fields.

#### **RESULTS**

## ONLINE UNSUPERVISED SPATIO-TEMPORAL SPIKE PATTERN CLASSIFICATION

In the following sections the classification performance of SKAN is tested in several ways. For these tests equally likely spatio-temporal spike patterns, each with one spike per channel per presentation were presented in random sequences to the SKAN network. **Table 1** details the parameters used in all the tests. These parameters were deliberately chosen for non-optimized

performance so as to try to mimic the use of the system in the wild by a non-expert user. Examples of available optimizations include: higher ddr values which result in faster converging systems, reduced  $\Theta_{rise}/\Theta_{fall}$  ratio for improved robustness to noise, increased  $\Delta r_{max}/\Delta r_{i,n}(t=0)$  ratio and increased pattern widths for enhanced pattern selectivity.

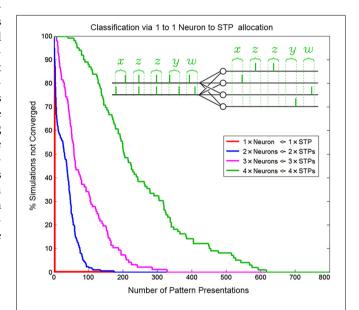

## Hardware efficiency through 1-to-1 neuron to pattern allocation at the local level

Through temporal competition a local network of mutually inhibiting SKANs can efficiently distribute limited neural resources in a hardware implementation to observed spatiotemporal patterns as is demonstrated in **Figure 14**.

FIGURE 14 | Convergence rate of as a function of neuron/pattern numbers and number of pattern presentations for a 1-to-1 two input neuron to pattern allocating network. As the number of patterns/ neurons increases the system requires longer pattern sequences to correctly allocate exactly one unique pattern to each neuron. The inset shows the five consecutive correct classifications of four patterns by four neurons.

Table 1 | Parameter values used for all results.

| Parameter                | Value                   | Description                                                                                                          |  |

|--------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------|--|

| ddr                      | 1                       | Change in the kernel step size. Higher value results in faster adaptation; lower values are more robust to noise     |  |

| w(r <sub>max</sub> )     | 10,000                  | Maximum kernel height (synaptic weight)                                                                              |  |

| r <sub>min</sub>         | 0                       | The kernel signal r(t) saturates at zero                                                                             |  |

| $\Delta r_{i,n}(t=0)$    | $100 \times (1 + rand)$ | Initial kernel step size (For each input <i>i</i> to each neuron <i>n</i> )                                          |  |

|                          |                         | The randomized initialization allows different neurons to learn different patterns                                   |  |

| $\Delta r_{max}$         | 400                     | Maximum kernel step size                                                                                             |  |

| $r_{i,n}(t=0)$           | 0                       | Initial kernel value                                                                                                 |  |

| $\Theta_{\it rise}$      | 40 × inputs             | Rise in threshold during output spike, where inputs is the number of input channels per neuron                       |  |

| $\Theta_{\mathit{fall}}$ | 100 × inputs            | Fall in threshold due to input spikes, where inputs is the number of input channels per neuron                       |  |

| inh <sub>max</sub>       | 100                     | Initial value of the inhibitory countdown                                                                            |  |

| inh <sub>decay</sub>     | 1                       | Step size of the inhibitory countdown. As a rule of thumb use: $inh_{max}/inh_{decay} = min[\Delta r_{i,n} \ (t=0)]$ |  |

| T                        | 400 Δ <i>t</i>          | Time between pattern presentations                                                                                   |  |

Similar to biological systems, in a SKAN network there is no supervisor switching the network from a training mode to a testing mode so there is no distinction between learning and recognition. This means that attempting to test SKANs in the traditional neural network sense by switching off a network's adaptation mechanisms would disable the system. Thus, to test the network's performance 1000 simulations were generated for each instance of the network, with up to 800 pattern presentations each. The network was considered to have converged to a stable solution when 20 consecutive patterns were correctly classified by the network, i.e., with a single neuron responding per spatiotemporal pattern. This is illustrated in the inset of **Figure 14**. Correct classification was defined as the case where a neuron spikes if and only if its target pattern is presented and where the neurons consistently spike for the same learnt target pattern. Also, a single neuron should spike once for each input pattern and no extra output spikes occur. The percentage of simulations that had not converged to correct classification was recorded as a function of the number of patterns presented, and is shown in Figure 14. Simulations were terminated once a network had converged. The number of consecutive patterns was chosen as 20 to reduce the likelihood that the observed "correct" response of the network was due to chance.

## Classification performance as a function of spatio-temporal pattern dimension

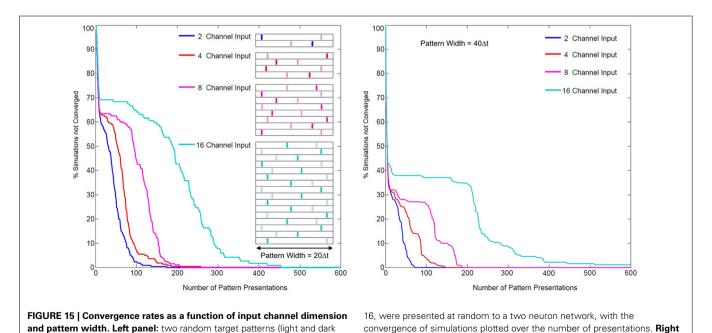

The problem of coordinating multiple synapses for unsupervised neuronal classification in SNN models, whether through simply learning synaptic weights or through more complex pathways, is difficult (Jimenez Rezende and Gerstner, 2014). In SKAN the hybrid synapto-dendritic kernel adaptation produces convergence profiles shown in **Figure 15**. These results show how the convergence profiles of SKAN change with the number of active

input channels. Additionally, the right panel in **Figure 15** shows the effect of increasing the resolution of the spatio-temporal pattern. Doubling the number of time steps in the maximal width of the target pattern *PW*, results in improved convergence profiles.

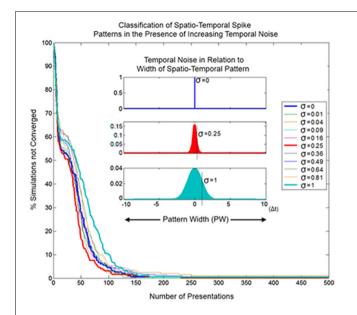

#### Classification in the presence of temporal noise

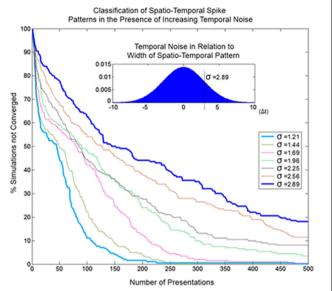

In order for SKAN to operate as an effective classifier competing neurons must balance the requirements of selectivity and generalization. In the spatio-temporal context, generalization takes the form of temporal jitter noise. In this context neurons must recognize patterns closest to their learnt target pattern despite the presence of temporal noise, while not recognizing other similarly noise corrupted patterns that are closer to the target patterns learnt by other neurons. Furthermore, the neurons should not expect the learning phase to be any less noisy than the testing phase or even for there to be any such distinct separation between learning and recognition. As well the neurons should maintain their correct learning and recognition behavior across a wide range of noise levels and they should ideally do so without the requirement for external adjustment of their parameters. SKAN satisfies all these requirements. The classification performance of SKAN is robust to temporal jitter noise as illustrated in **Figure 16** where two neurons act as two Kalman filters with shared inputs attempting to learn the statistics of two noisy but distinct ISI generating processes.

Because of the constant adaptation of the neurons, moderate levels of temporal noise with standard deviation up to  $\sigma = 0.25$   $\Delta t$ , which is 1/80th of the pattern width, either do not affect or actually *improve* SKAN performance. With high temporal noise levels, i.e., with a standard deviation that is 1/20th the width of the pattern ( $\sigma = 1$   $\Delta t$ ), the convergence profile is still similar to that of the noiseless case. Such levels of temporal noise can disable a conventional processor and even some neural networks. Even at the

**panel:** the same test with maximal pattern width  $PW = 40 \Delta t$ .

bars) of maximal pattern width  $PW = 20 \Delta t$  and of dimensions 2, 4, 8, and

FIGURE 16 | Convergence as a function of temporal noise and pattern presentations in a two neuron network with two input channels.

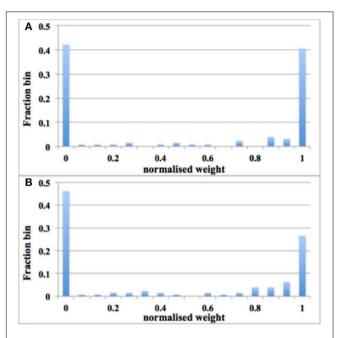

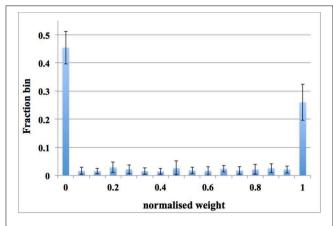

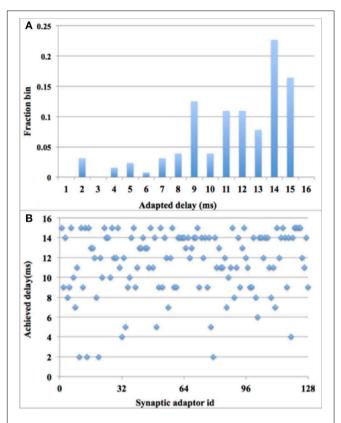

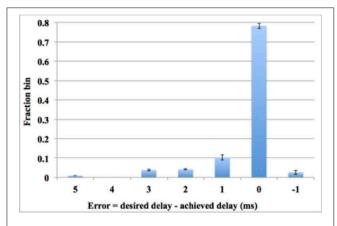

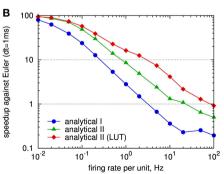

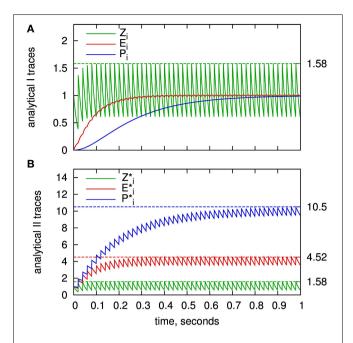

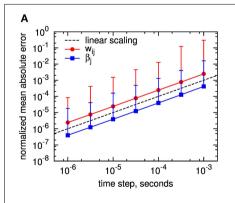

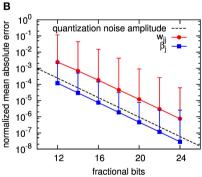

The insets illustrate selected noise distributions relative to the maximal pattern width ( $PW=20~\Delta t$ ). The left panel shows convergence profiles