- 1College of Microelectronics, Beijing University of Technology, Beijing, China

- 2Beijing Academy of Blockchain and Edge Computing, Beijing, China

In recent years, thanks to the development of integrated circuits, clinical medicine has witnessed significant advancements, enabling more efficient and intelligent treatment approaches. Particularly in the field of neuromedical, the utilization of brain-machine interfaces (BMI) has revolutionized the treatment of neurological diseases such as amyotrophic lateral sclerosis, cerebral palsy, stroke, or spinal cord injury. The BMI acquires neural signals via recording circuits and analyze them to regulate neural stimulator circuits for effective neurological treatment. However, traditional BMI designs, which are often isolated, have given way to closed-loop brain-machine interfaces (CL-BMI) as a contemporary development trend. CL-BMI offers increased integration and accelerated response speed, marking a significant leap forward in neuromedicine. Nonetheless, this advancement comes with its challenges, notably the stimulation artifacts (SA) problem inherent to the structural characteristics of CL-BMI, which poses significant challenges on the neural recording front-ends (NRFE) site. This paper aims to provide a comprehensive overview of technologies addressing artifacts in the NRFE site within CL-BMI. Topics covered will include: (1) understanding and assessing artifacts; (2) exploring the impact of artifacts on traditional neural recording front-ends; (3) reviewing recent technological advancements aimed at addressing artifact-related issues; (4) summarizing and classifying the aforementioned technologies, along with an analysis of future trends.

1 Introduction of the artifacts in CL-BMI

1.1 Mechanism of BMI

Brain-machine interface (BMI) technology can restore communication and control to people who are severely paralyzed (McFarland et al., 2017). A typical BMI system consists of a power management module, a neural recording unit, a signal processing module to convert the neural signal recorded into a control signal, and an external effector device (such as haptic or tactile stimulator, etc.) to achieve stimulation. By acquiring neural signals at the front end of the damaged nerve can be divided into implantable data collection (electrode) and non-implantable data collection (functional magnetic brain imaging or functional near-infrared spectroscopy, etc.). Then BMI analysis them, and control the stimulator to stimulate the back end of the damaged nerve. This system will recover the lost function caused by the damage in the central or peripheral nerve system (Chen et al., 2022).

1.2 Mechanism of artifacts formation

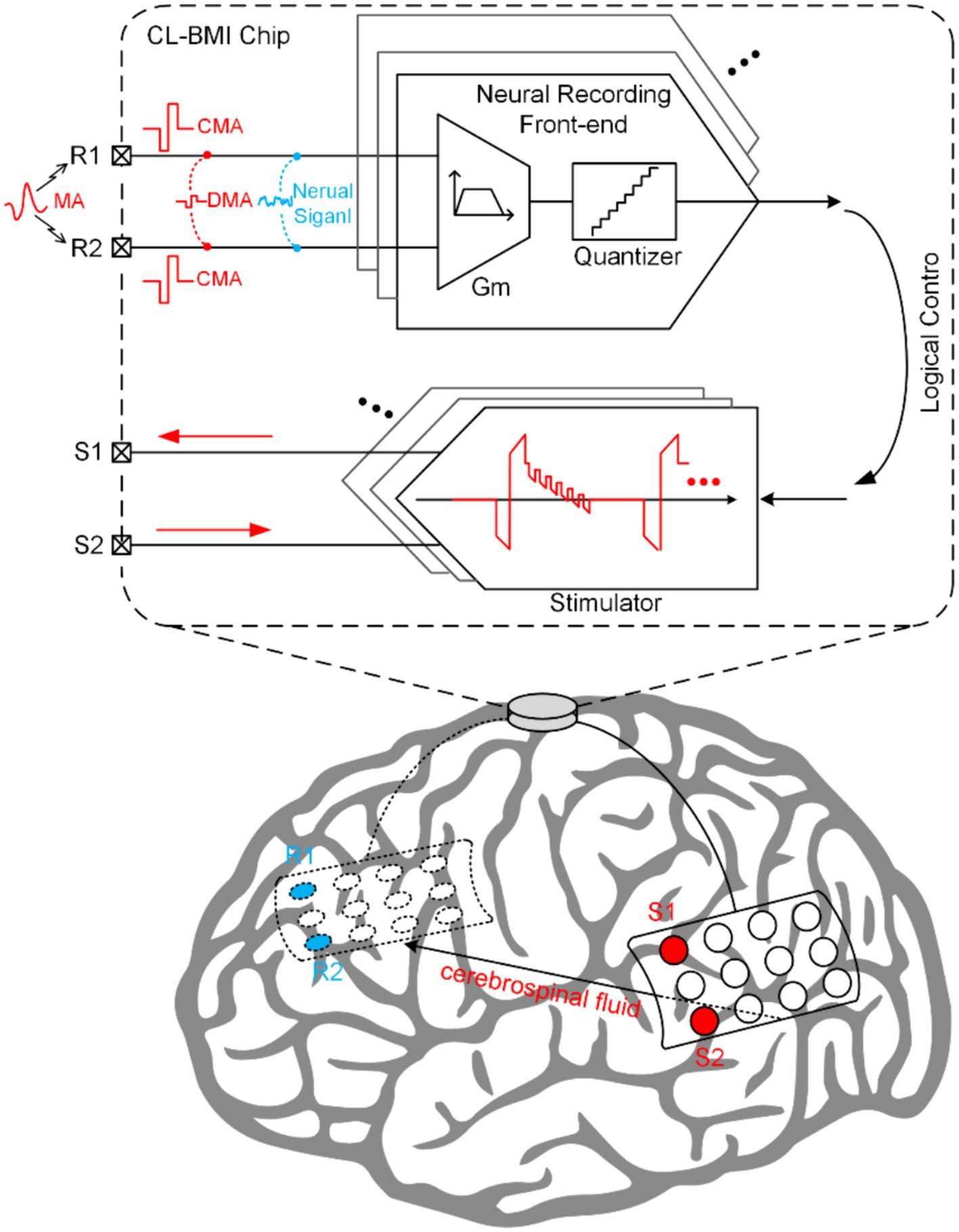

In vivo neural recordings often encounter various artifacts, undermining the capture of essential neural signals, particularly in less constrained recording environments (Islam et al., 2012, 2014). These artifacts can be broadly classified into two types: motion artifacts (MA) and SA. MA arise from factors such as respiration, electrode impedance changes, and body movements, posing significant challenges for wearable biomedical recording devices (van Helleputte et al., 2014). Unique to CL-BMI, SA are generated by the concurrent stimulation and recording during closed-loop control. The stimulation pulses are coupled through the tissue impedance, resulting in the formation of SA at the input of the recording site (Chandrakumar and Marković, 2017a,b,c). These SA can be further categorized into common-mode artifacts (CMA) and differential-mode artifacts (DMA), depending on their impact on the neural signal (Pérez-Prieto et al., 2019).

As depicted in Figure 1, within the CL-BMI system, neural signals are accompanied by various artifact interference signals, which serve as input signals for NRFE. Consequently, during the design phase, designers must thoroughly evaluate the amplitude-frequency characteristics of diverse signals and the performance of neural recording front-ends to ensure a more informed and rational design approach.

1.3 Characteristics of artifact signals

Considering the formation mechanism of MA, it becomes evident that their amplitude and frequency are random, exhibiting a large dynamic range compared to the measured biopotential. Moreover, the bandwidth of MA may extend well within the biopotential signal bandwidth (Debbarma and Bhadra, 2022). Thus, the characteristics of MA necessitate evaluation through real-world experiments.

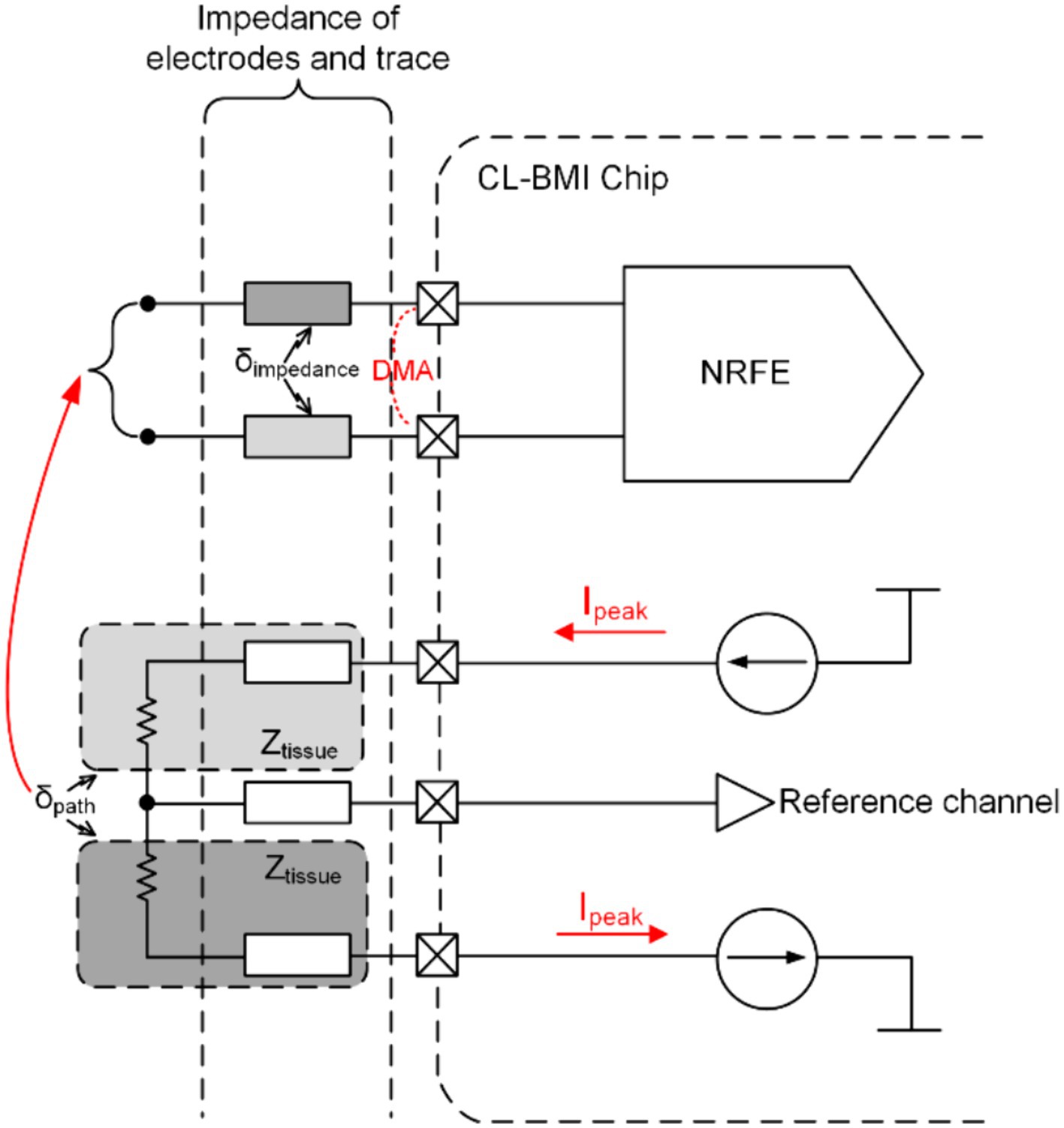

For the evaluation of SA, modeling of CL-BMI system can be employed, as depicted in Figure 2. This figure illustrates how the stimulation signal from a fully differential stimulator (FDS) generates SA through the direct conduction path of cerebrospinal fluid (CSF) and capacitive coupling from the electrode to the recording electronics, ultimately reaching the recording input site (Chandrakumar and Marković, 2017a,b,c). Notably, the FDS is utilized to mitigate artifact interference at the stimulation side (Liu et al., 2017; Pu et al., 2021), and SA occupy the same frequency band as the neural signal (Chandrakumar and Marković, 2017a,b,c). This model utilizes peak stimulation current amplitudes () and the impedance of the direct conduction path () to determine the peak-to-peak stimulation voltage swing () for one path of the FDS.

Considering the path mismatch in the output of FDS due to process and complex environmental factors (with the mismatch coefficient denoted as ), the peak-to-peak amplitude of FDS’s output (representing the CMA voltage, CMAV) is expressed by the formula:

For recordings with fully differential inputs or those featuring reference channels, DMA arises due to impedance mismatch in the direct conduction path and electrodes (with the mismatch coefficient denoted as ), and its voltage amplitude (DMAV) is denoted as:

Using recent publication (Li et al., 2023) on related application stimulators as an example, with and , assuming worst-case scenarios of 0.5 and , the resulting CMA and DMA are 750 mV and 75 mV, respectively.

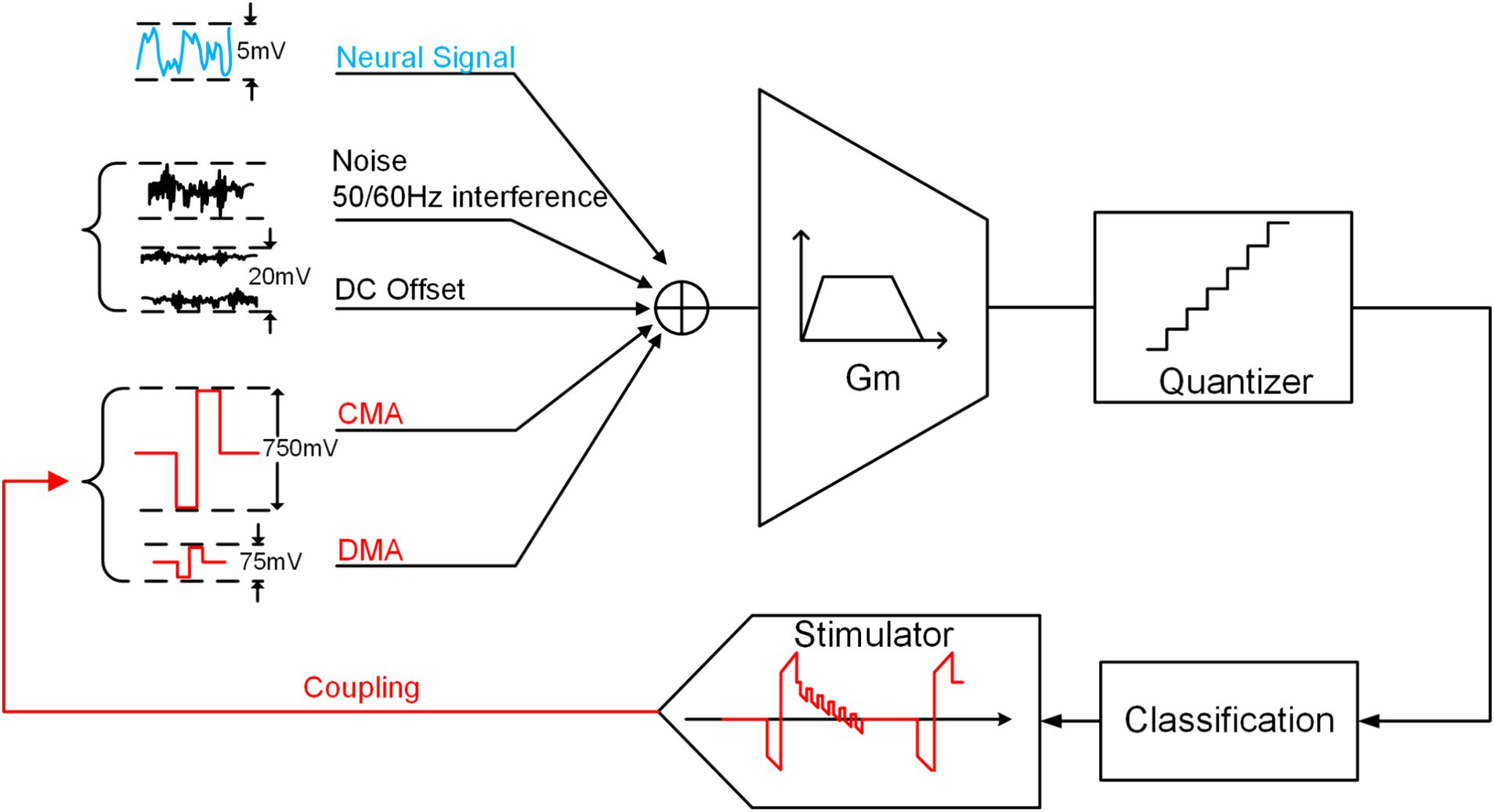

The neural signals of interest are typically categorized into two types: local field potentials (LFP) and action potentials (AP). The frequency range of LFP is 1 to 100 Hz, with an amplitude of approximately 5 mV, while APs have a frequency range of 100 to 7 kHz, and an amplitude of approximately 100 (Harrison and Charles, 2003). As depicted in the figure, traditional NRFE may introduce interference or even annihilation of neural signals in practical applications due to the presence of artifact signals with amplitudes in the range of several hundred millivolts.

2 The influence of artifacts on prior research

Building on the analysis in the previous section, we can simplify the NRFE structure in CL-BMI, as depicted in Figure 3. Besides artifacts, the analog front end is susceptible to noise, offset voltages and 50/60 Hz interference, etc. (Verma et al., 2010). Although conventional neural recordings can eliminate these interferences, they may still be susceptible to artifacts that saturate the output.

2.1 Overview of the system requirement and the state-of-the-art

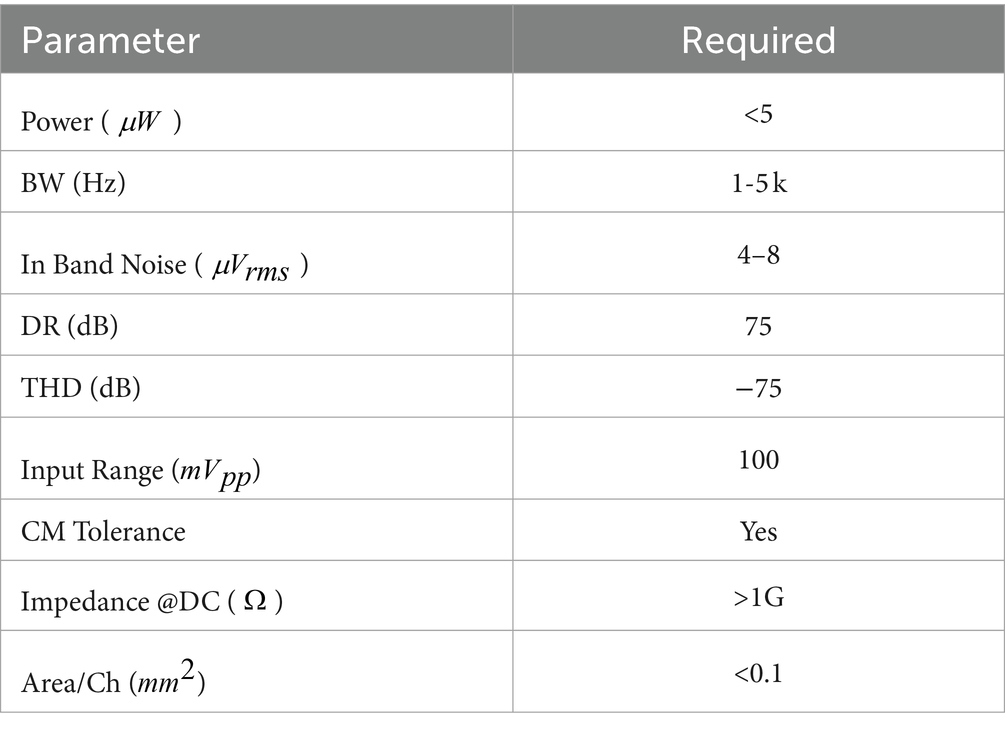

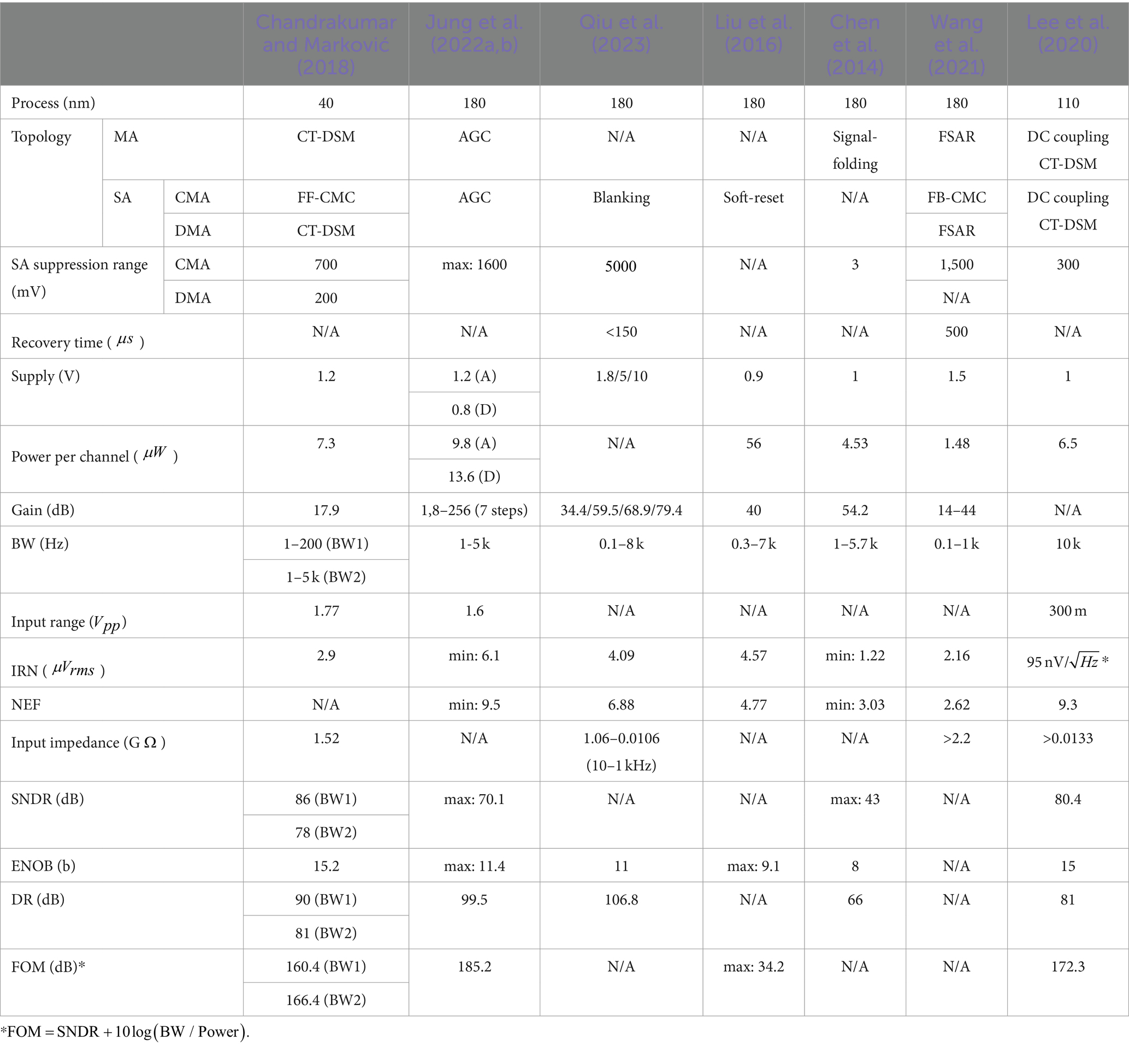

In the context of practical applications, designing NRFE system requires meeting various system requirements. Table 1, summarized from recent literature (Chandrakumar and Marković, 2017a,b,c; Liu et al., 2020), outlines these essential requirements.

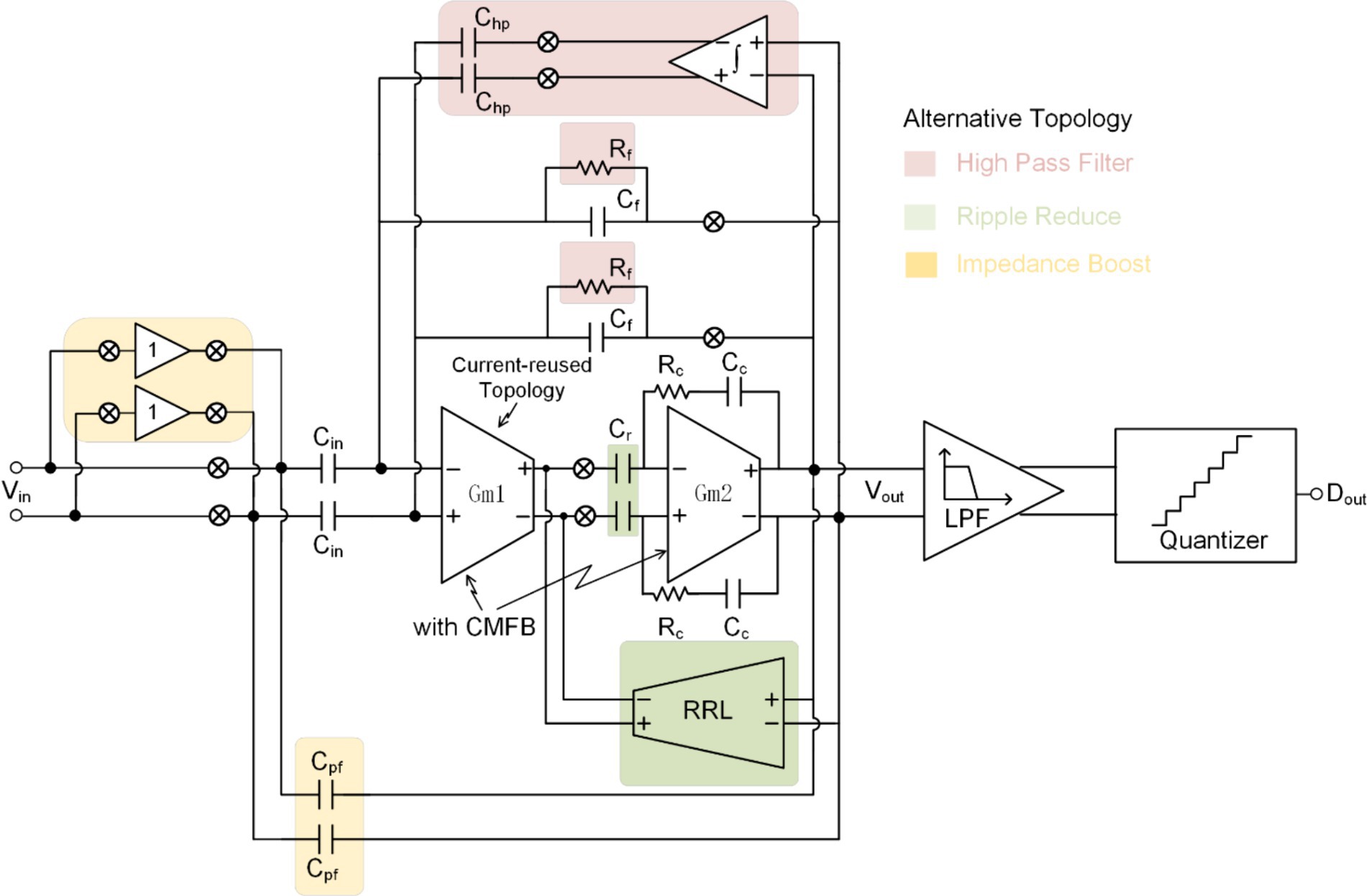

Over the past two decades, extensive research on neural recording front-ends has been conducted, with continuous refinement (Oh et al., 2008; Zou et al., 2009; Fan et al., 2011; Zou et al., 2013; Mondal and Hall, 2017). Novel techniques and topologies of NRFE (illustrated in Figure 4) have emerged to optimize specific system requirements outlined in Table 1.

Figure 4 illustrates a complete neural recording front-end system featuring a capacitively-coupled chopper instrumentation amplifier (CCIA). The amplification and acquisition module of CCIA typically employs a two-stage operational amplifier structure, with the first stage commonly utilizing current-reuse technology to minimize the system’s input referred noise (IRN). To mitigate the DC offset introduced by the electrode, it is necessary to establish a high-pass cut-off frequency for the neural recording. To address ripple caused by the offset of the first stage of the neural recording, ripple reduction technology is necessary, achievable by connecting capacitors in series between two stages or introducing ripple reduction loop (RRL). Chopping technology significantly reduces the equivalent input impedance of the neural recording front-end and induces signal attenuation. Hence, impedance enhancement technology becomes necessary. Auxiliary charging path and positive feedback capacitors are both viable options.

While these techniques and structures are susceptible to artifacts, as highlighted in the previous analysis, they lay the foundation for the application of neural recordings in CL-BMI. By addressing specific system requirements, these advancements contribute to the ongoing progress in neural recording technology.

2.2 Tolerance of artifacts interference

As previously described, artifacts in neural recordings can be categorized into two types: CMA and DMA. This section will elaborate on their distinct impacts on traditional NRFE.

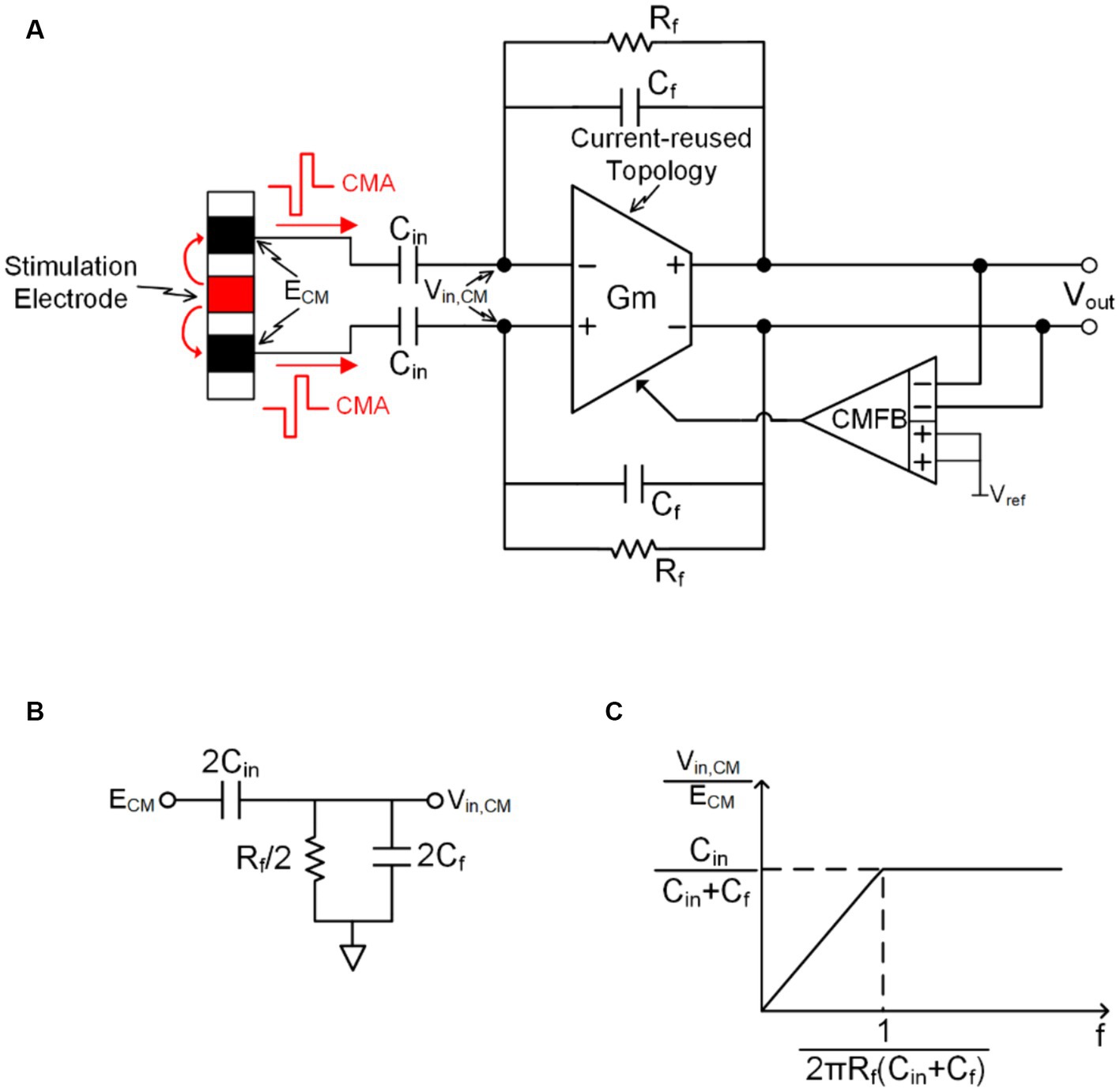

Taking the fully differential capacitive negative feedback model illustrated in Figure 5A as an example, when the CMA, approximately 750 mV as discussed before, is present at the input of the recording electrode, it directly influences the signal at the output due to its nature as a common-mode (CM) swing signal. Fully differential amplifiers (FDA) typically utilize a common-mode negative feedback (CMFB) circuit to stabilize the output CM voltage (Zhang et al., 2018). Consequently, for CM signals, the output of FDA can be considered equivalent to AC ground. The equivalent CM circuit is depicted in Figure 5B. From this, we can derive the transfer function from the CM input signal at the electrode input end to the FDA input end. Therefore, the transfer function from the CM input signal at the electrode input site to the FDA input site can be derived.

where is the CM input signal at the FDA input side and is the CM input signal at the electrode input side.

Figure 5. (A) CM response of conventional capacitive feedback neural recording. (B) The simplified CM response circuit. (C) Transfer function of the CM response.

The graph of the transfer function (Figure 5C) indicates that the model of CM voltage transfer across the recording electrodes can be considered as a first-order high-pass filter, with its corner frequency determined by . In practical applications, this corner frequency is approximately 10 Hz. Therefore, CMA at the same frequency band as the neural signal can be transmitted to the input of FDA without attenuation. However, the amplitude of CMA far exceeds the input common-mode range (ICMR) of the FDA, resulting in saturation distortion in the FDA output. Despite employing amplifier topologies with a large common-mode input range, such as rail-to-rail or folded cascode topologies, total harmonic distortion (THD) at the neural recording front-end can still increase when artifacts are present at the input site. In cases of significant THD, the effective number of bits (ENOB) and signal-to-noise and distortion ratio (SNDR) of the quantization module will significantly deteriorate, leading to data conversion errors (Xu et al., 2018).

In general application neural recording front-ends, gains are typically set to more than 40 dB to amplify neural signals for quantification and processing. However, in the context of CL-BMI systems, DMA are also amplified by the neural recording front-end. As previously mentioned, the amplitude of DMA is approximately 75 mV, and maintaining the gain would also lead to output saturation.

It is evident that the introduction of CMA or DMA to the input site of NRFE leads to output saturation and distortion. However, considering their formation mechanism and signal nature, methods exist to shield the neural recording front-end from their interference.

3 Anti-artifacts technology

This section will introduce anti-artifact technologies developed over the past two decades. It is important to note that these technologies address a range of artifact issues, including MA and SA, each with distinct application backgrounds. However, despite the differences in application context, the consistent nature of the artifact signals allows for a unified approach in this section.

As mentioned previously, artifacts introduce nonlinear factors into neural recording front-ends due to their relatively high amplitude compared to neural signals and the limited dynamic range of the recording systems. Therefore, most anti-artifact technologies primarily focus on improving dynamic range and linearity and eliminating artifacts through back-end signal processing algorithms. Additionally, the periodic nature of artifacts is crucial for their effective elimination, further emphasizing the importance of advanced signal processing techniques in artifact mitigation strategies.

3.1 Current compensation technology utilized in rail-to-rail amplifiers

The most direct way to overcome common-mode artifact interference is to increase the input common-mode range (ICMR) to ensure that the neural amplifier can operate normally at higher common-mode input voltages. The rail-to-rail topology enables the widest possible input common-mode range, and a constant equivalent input transconductance can be achieved through current compensation techniques (Huang et al., 2022).

As mentioned in (Chandrakumar and Marković, 2017a,b,c), even if linearity can be preserved when the ICMR is larger than the amplitude of CMA, THD degraded when CMA was enabled. This distortion can be especially noticeable in systems with low noise and low power requirements such as neural recording. Therefore, simply improving ICMR is not advisable.

3.2 Moderate gain recording amplifier with high resolution ADC

One approach to increase dynamic range is to reduce the gain to prevent saturation of the neural recorder. However, if the gain is very low, it will bring challenges to the design of the ADC. This occurs due to the extremely low system gain inherent in this topology, resulting in an SNDR lower than the ADC in the same topology with a high-gain IA when the same amplitude signal is input. Considering that artifacts are amplified alongside neural signals, the ADC necessitates sufficiently high ENOB and SNDR to accommodate a broad signal input range.

Chandrakumar and Marković (2018) demonstrates a CCIA using a chopper-stabilized structure with a moderate gain of only 17.9 dB (). This makes the required ENOB of the proposed neural recording front-end larger than 15 bits and the required SNDR of 13 bits. Its ADC structure uses a continuous-time (CT) delta-sigma (DS) ADC structure, which has good power efficiency when ENOB15 bits. The details of CT-DS technique will be described at the end in this section.

The disadvantage of this technology is that it is only immune to the influence of DMA, and its ability to tolerate DMA amplitude is limited due to the constraints of gain and dynamic range of the instrumentation amplifier (IA). In addition, the power consumption of this structure is higher than that of traditional high-gain IA and low-resolution ADC structures. This is because a low-gain IA cannot effectively mitigate the impact of quantization noise. Hence, opting for a high-resolution ADC is important, although at the expense of significantly elevated power consumption. (Jung et al., 2022a,b).

3.3 Adaptive gain control (AGC)

Since the artifact is generated by the stimulation current which is generated periodically in the CL-BMI system, the artifacts are also periodic signal. The stimulation cycle is very short compared to the entire neural signal acquisition period. Therefore, the performance of a fixed low-gain IA is not ideal during non-stimulation periods. The use of AGC technology allows the IA to perform varying gain adjustments according to the input signal amplitude to solve this issue (Delgado-Restituto et al., 2017).

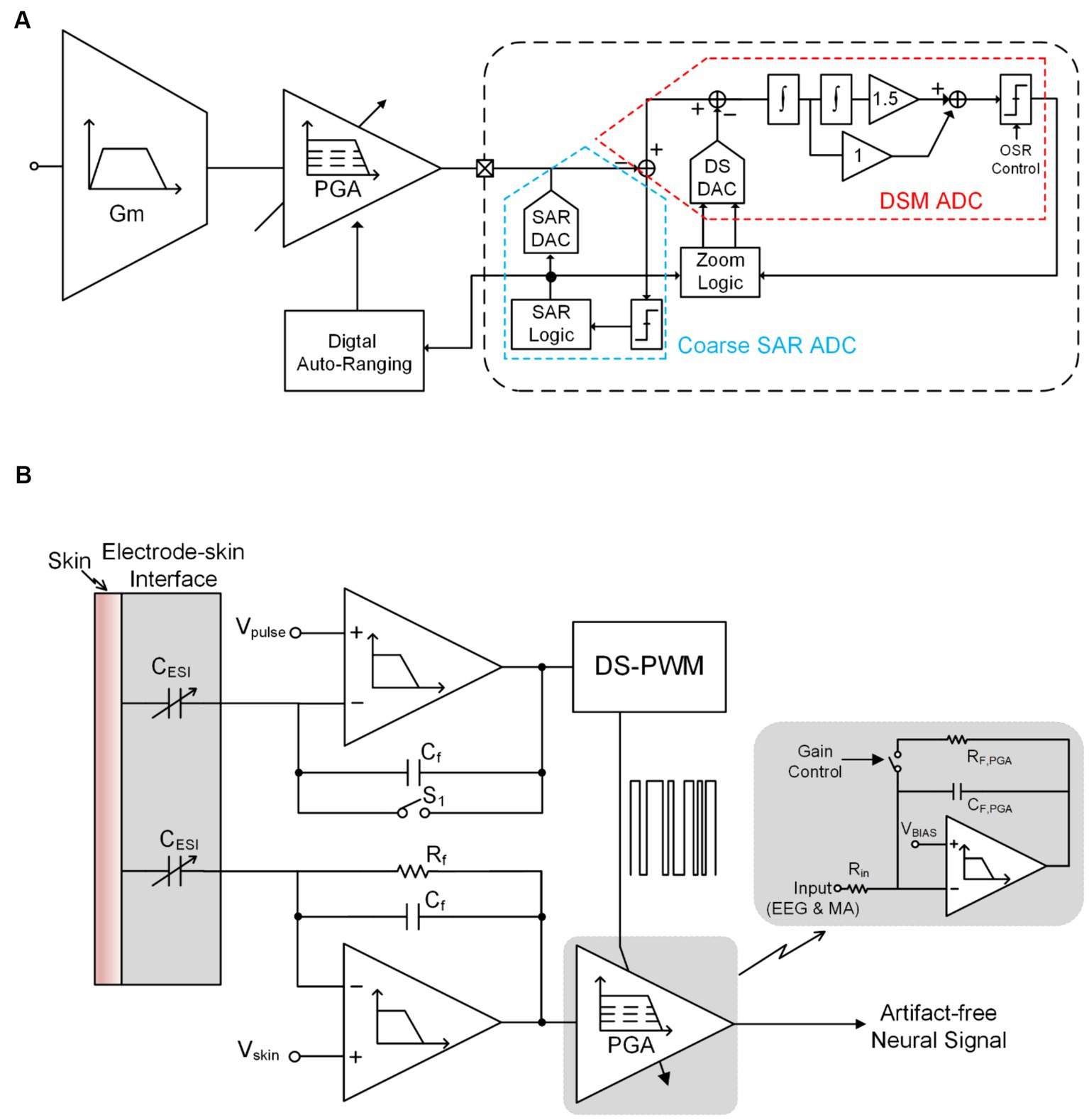

Building upon the improvement of the previous technology, Figure 6A depicts AGC technique that utilizes SAR ADC reused in CT-DS modulator (CT-DSM) and digital auto-ranging (DAR) technology to control programmable gain amplifier (PGA) gain, thereby avoiding neural recording front-end saturation (Jung et al., 2021, 2022a,b). This system consists of a low gain instrumentation amplifier (IA), a PGA, a CT-DSM and a DAR block. The IA gain is fixed of 8 and the PGA gain is automatically controlled from 1 to 32 by DAR and CT-DSM depending on the input signal amplitude.

Figure 6. (A) AGC technique that utilizes SAR ADC reused in CT-DS modulator and DAR technology to control PGA gain. (B) the gain of low path’s (LP’s) PGA controlled by the up path’s (UP’s) output through a DS-pulse-width-modulation block.

Figure 6B shows another AGC topology (but this topology is only applicable to MA), which the top-level block diagram of the gain of low path’s (LP’s) PGA controlled by the up path’s (UP’s) output through a DS-pulse-width-modulation (DS-PWM) block (Dabbaghian and Kassiri, 2023). The DS-PWM is operating with a 100 kHz frequency to guarantee well compensate the input artifact signal in real-time. The duty cycle of DS-PWM output (D) can be expressed as:

Where is constant determined by the relationship between , (when PWM output (D) is zero, the DAC’s output is VP2 and when PWM output is VDD, the DAC’s output is VP1.), and ; variations caused by random motion.

The gain of the overall neural recording front-end is independent of motion variation term , and can be derived as:

where is the feedback resistor of PGA and is the input resistor of PGA as shown in Figure 6B.

According to the description in (Pérez-Prieto, N. et al., 2019), there are two problems: Firstly, the larger the variable range of the PGA gain, the more complexity will increase in the digital reconstruction algorithm; secondly, according to the way the PGA changes the gain, it can be seen that the input-referred noise and bandwidth of the PGA will change under different gains.

3.4 Blanking

Due to the periodicity of SA, shutting off neural signal input during the neural stimulation cycle is an effective anti-artifact strategy. The technology of acquiring and processing neural signals outside of the stimulation cycle is collectively called blanking (Bi et al., 2020; Debarros et al., 2020; Huang et al., 2023; Qiu et al., 2023).

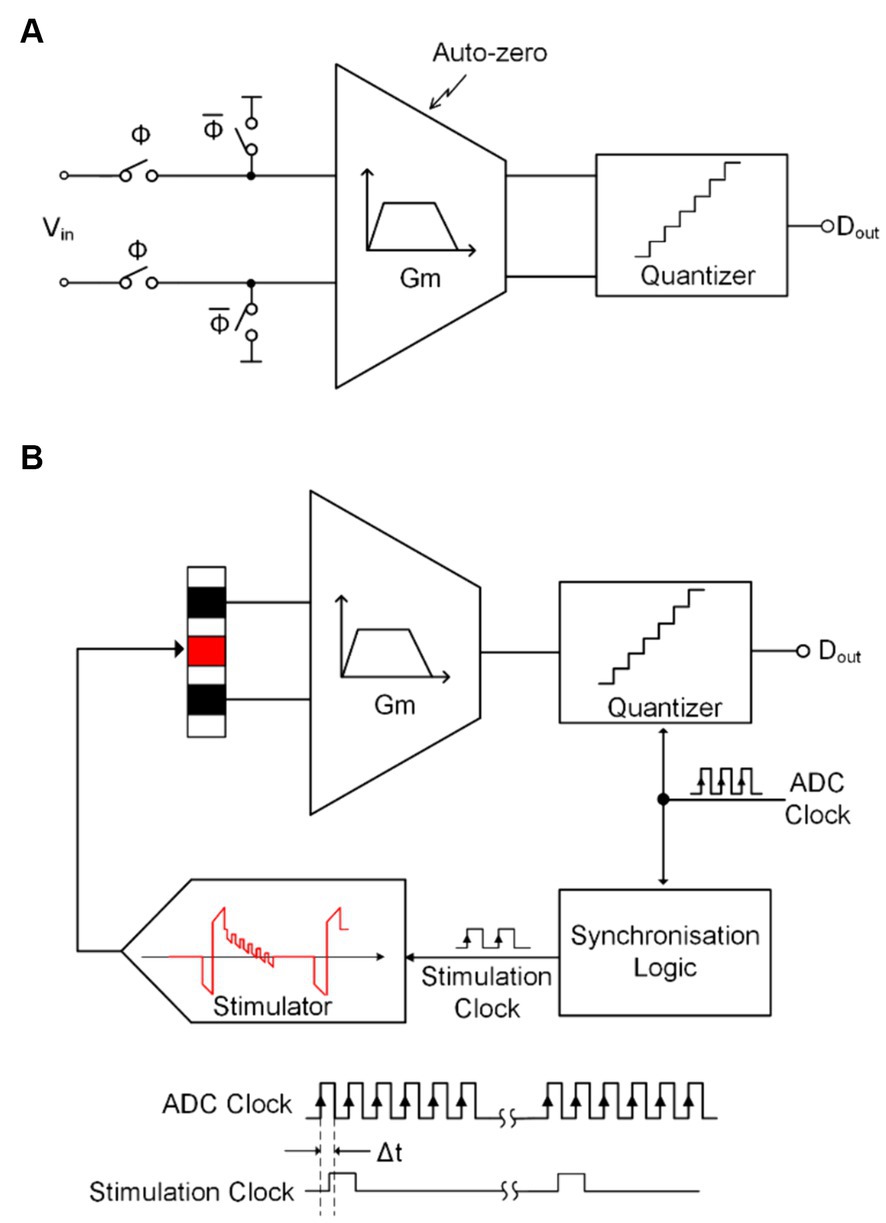

Figure 7A shows one of the structures that implements blanking at the input end of the neural amplifier (Bi et al., 2020; Huang et al., 2023; Qiu et al., 2023) achieve the shielding function of artifact signals by generating a synchronous clock during the stimulation cycle to control the sampling switch at the input end. It is worth noting that when controlling the on/off of the sampling switch, a certain time interval should be preserved. Therefore, the entire blanking time can be expressed as:

Where is the inter-phase gap time interval between negative and positive pulses in biphasic constant current stimulation (CCS) and is the negative (positive) stimulation pulse width.

Figure 7. (A) The block diagram of the conventional blanking technique. (B) The block diagram of blanking with synchronization logic.

Different from the method of shielding artifact signals at the input end, (Debarros et al., 2020) proposed a technology that simultaneously controls the ADC sampling clock and stimulation clock through a synchronous logic unit to achieve the shielding of artifact signals. In this work, the stimulation pulses happen between two ADC samplings, so it guarantees the ADC holds the recoding to its previous voltage before each stimulation pulse, as shown in Figure 7B.

On the one hand, Blanking technology will cause the information of the stimulation cycle to be lost and it is difficult to recover quickly after the stimulation cycle; on the other hand, when the switch is on, noise will be introduced at the input end (Erez et al., 2010).

3.5 Soft-reset

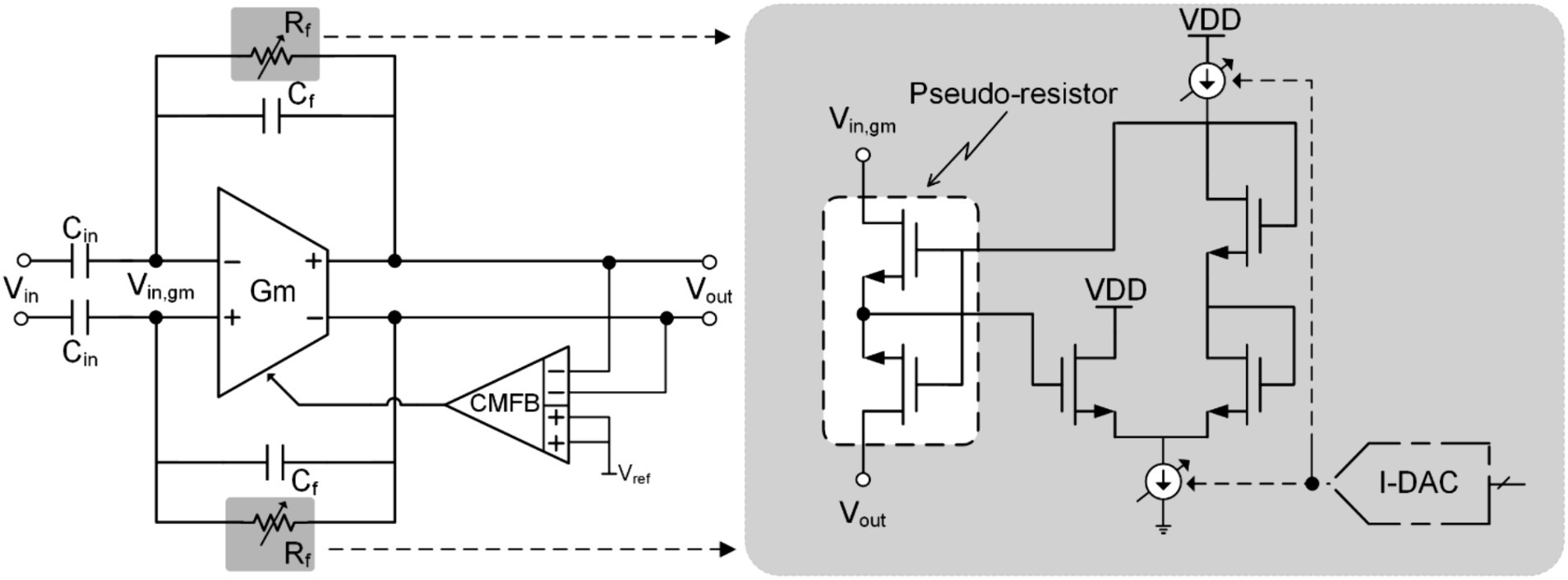

Similar to Blanking technology, soft-reset technology also uses the periodicity of artifacts to shield them (Liu et al., 2016; Viswam et al., 2016; Shadmani et al., 2019; Erbsloh et al., 2021). The difference is that blanking technology performs shielding in the time domain, while soft-reset technology performs shielding in the frequency domain.

Figure 8 shows the schematic of soft-reset technology. It modifies the high-pass cutoff frequency by controlling the current in the pseudo-resistor in the capacitive feedback amplifier, thereby reducing the gain of the neural amplifier to avoid saturation. Therefore, this technology is also called pole-shifting. For a capacitive feedback amplifier, a pseudo resistor (Sharma et al., 2016; Guglielmi et al., 2020) is usually used to bias the DC operating point of the amplifier. At the same time, the pseudo-resistance will also introduce a low-frequency pole . During the stimulation cycle, the system will increase the adjustment current in the pseudo resistor to reduce the equivalent impedance, thereby increasing the high-pass cutoff frequency of the amplifier to the kHz level to reduce its gain. In addition, the time constant of the amplifier becomes very small at this time (approximately in the range of 100 (Erbsloh et al., 2021)). This allows the neural recording front end to quickly recover and function normally after the stimulation cycle ends.

Although soft reset (pole-shifting) technology has a faster recovery time than blanking technology, there is still a risk of losing important information. In addition, pseudo-resistor leakage current exists in practical applications, which will affect the DC operating point of the amplifier. Therefore, when using soft reset (pole-shifting) techniques, it is still necessary to consider the non-ideal factors introduced by pseudo-resistance during non-stimulation periods.

3.6 Signal-folding

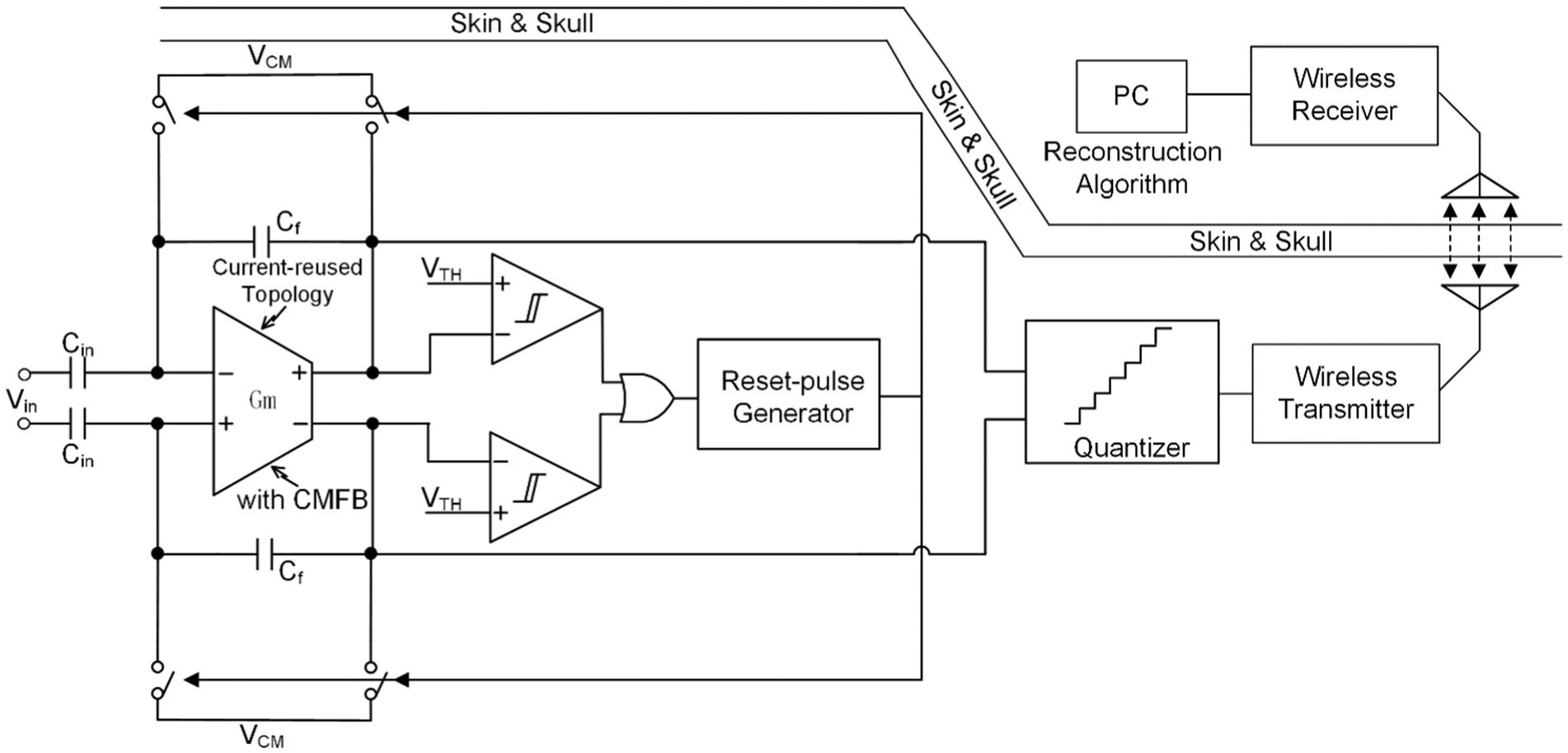

When the system applies blanking technology or soft reset technology, the recorded neural signal waveform will lose part of the information during the stimulation cycle. The signal folding technology can fold the signals before and after the stimulation cycle to specific values through a specific reset circuit topology, and then restore the signal through a reconstruction algorithm (Chen et al., 2014).

The signal folding concept is illustrated in Figure 9. Whenever at any time, the output signal falls below the threshold voltage , the circuit will generate a narrow-reset pulse signal to set the input and output voltages of the amplify-er to the reference voltage. Before and after the reset cycle, the output signal is folded into a voltage range of . In order to recover the amplified signal, a non-Nyquist reconstruction process is applied to the signal digitized by the ADC. This greatly relaxes the design requirements of the ADC.

Due to the slow settling time of the amplifier, signal-folding technology will still lose some information for a period of time after reset and cannot be recovered. In addition, the integration level of the system is greatly reduced by integrating a wireless communication module.

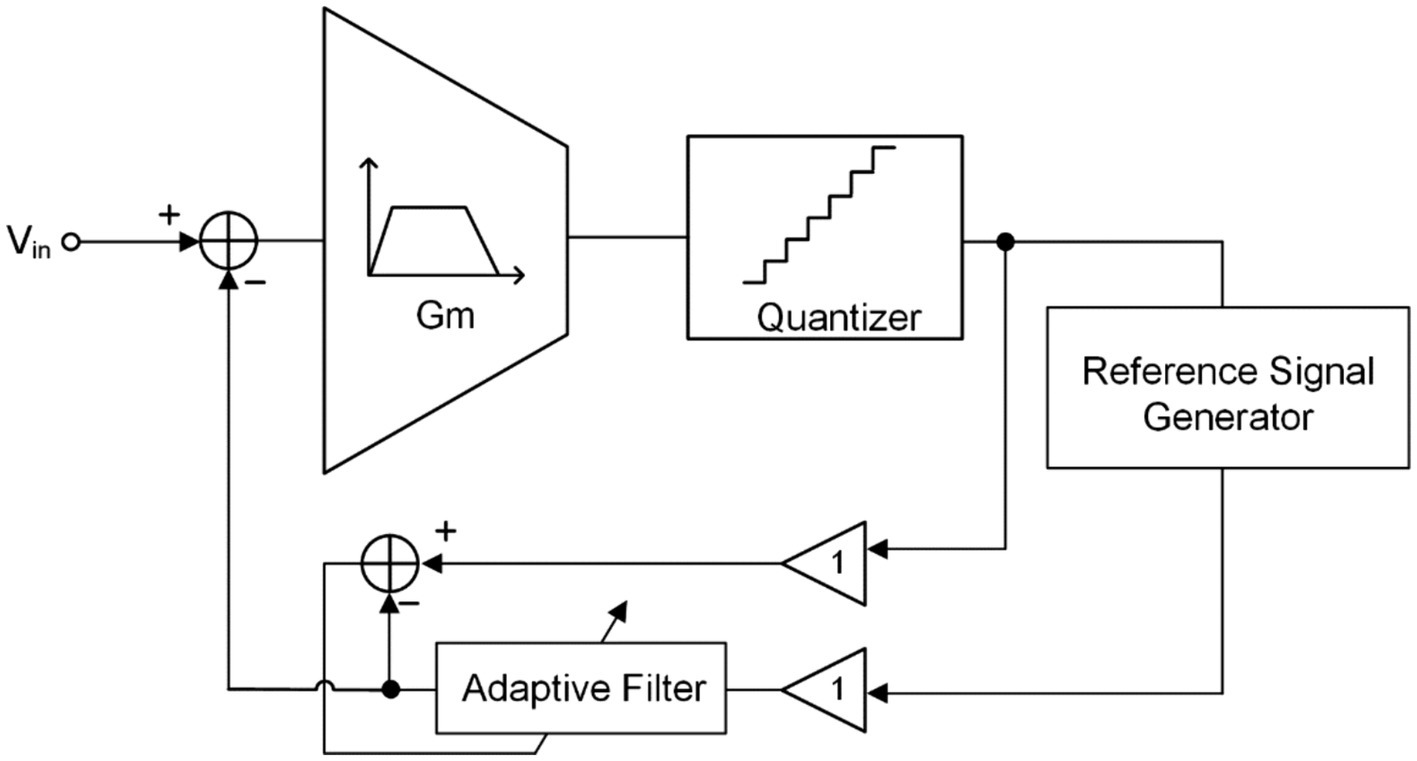

3.7 Adaptive filter

Similar to adaptive active noise cancelation technique (Sugiyama et al., 2011; Deb et al., 2014), the fast simulation artifact rejection (FSAR) technique eliminates artifact signals at the NRFE input end in the form of negative feedback through adaptive filter and reference signal generator, as shown in Figure 10 (Samiei and Hashemi, 2021; Wang et al., 2021). If a timely approximation of the artifact signal (or replica artifact signal) can be obtained through the reference signal generator, the accurate artifact signal can be obtained through the adaptive filter and fed back to the input. In this way, the artifact interference signals contained in the input signal can be eliminated, leaving behind the desired neural signal.

Figure 10. The block diagram of the fast stimulation artifacts rejection technique with adaptive filter.

Although NRFE can eliminate artifacts in digital domain by using adaptive filters, it can only eliminate DMA (or smaller amplitude artifacts) but will significantly reduce the DR of the system (Chandrakumar and Marković, 2017a,b,c).

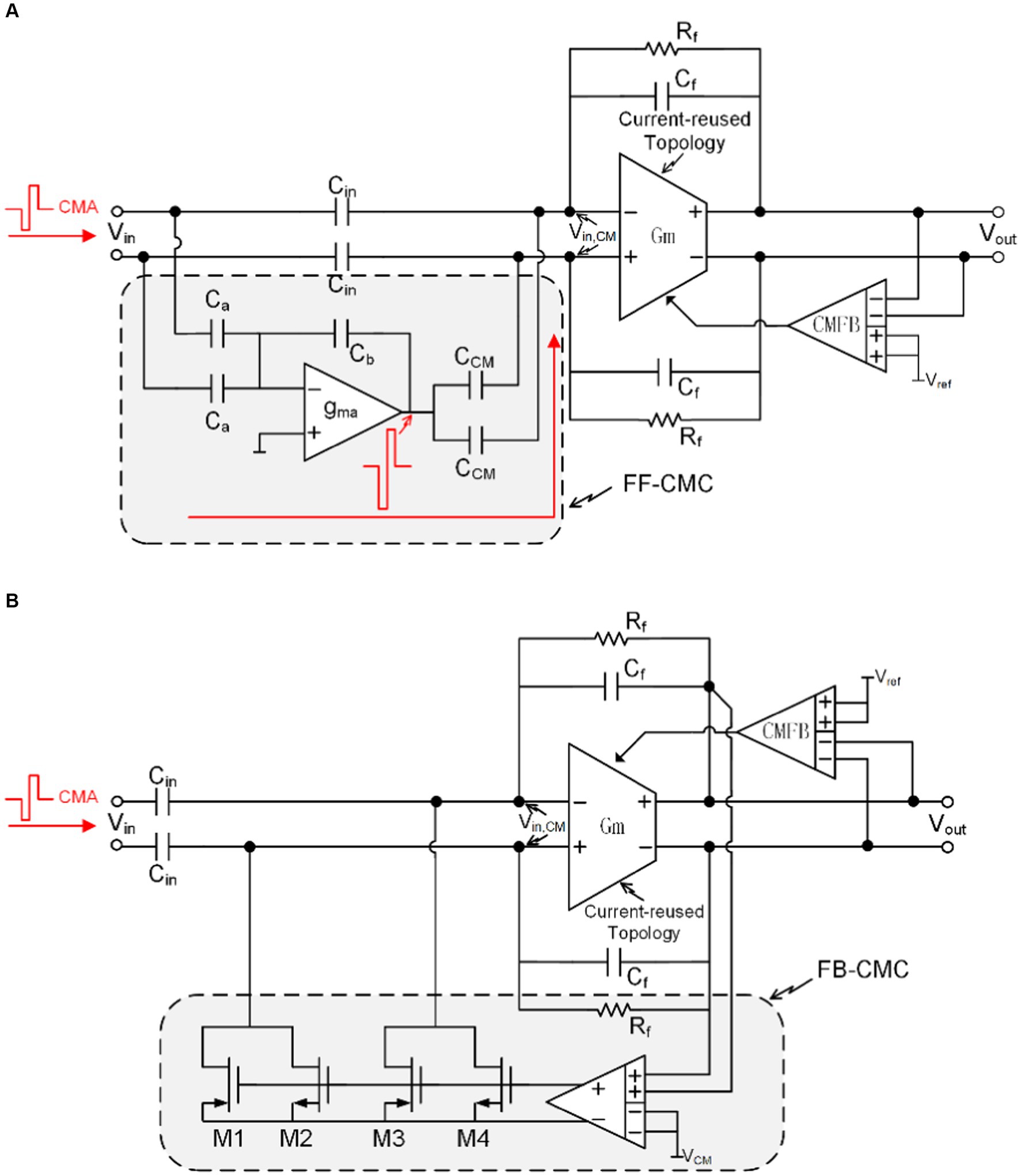

3.8 CM cancelation path

A CM feedforward topology can be used to eliminate the effects of CMA, referred to as feedforward CM cancelation (FF-CMC) (Chandrakumar and Marković, 2017a,b,c; Pham et al., 2022). The concept of FF-CMC path is shown in Figure 11A. The common-mode signals of the two recording electrodes in one channel are sensed and inversely amplified by a feedforward capacitive feedback adder (, , ) and summed at the input of the amplifier through capacitor . Among them, by rationally designing the sizes of the gain of the FF-CMC path () and, the effects of CMA can be completely eliminated:

Figure 11. (A) The block diagram of the feedforward common-mode cancelation path. (B) The block diagram of the feedback common-mode cancelation path.

To ensure accurate elimination of CMA, the bandwidth of the FF-CMC path needs to be much larger than k times the maximum frequency of the neural signal (). This requirement can be expressed by the following formula:

From this formula, we can get the design requirements of .

FF-CMC technology requires the capacitance in the path to be completely and accurately matched. Any mismatch will cause residual CMA to be introduced as DMA into the neural amplifier. This is the limitation of this technology. Fortunately, the neural amplifier is immune to smaller CM swing (<20 mV). Therefore, it is necessary to use common centroid technology in the layout to achieve a smaller mismatch ratio (<0.1%). In addition, the presence of the capacitors leads to an increase in the input-referred noise of the front-end (), as shown by the following equation:

is the input-referred noise of the neural amplifier . Therefore, the capacitance needs to be appropriately selected so that its input-referred noise meets the system requirements.

Feedback-CMC (FF-CMC) can also adjust the input common mode signal in real time through negative feedback (Wang et al., 2021). As shown in Figure 11B, if the output common mode level is greater than the reference common mode level, M1 and M3 will be turned on to reduce the input common mode level, and if the output common mode level is smaller than the reference common mode level, M2 and M4 will be turned on to enhance the input common mode level.

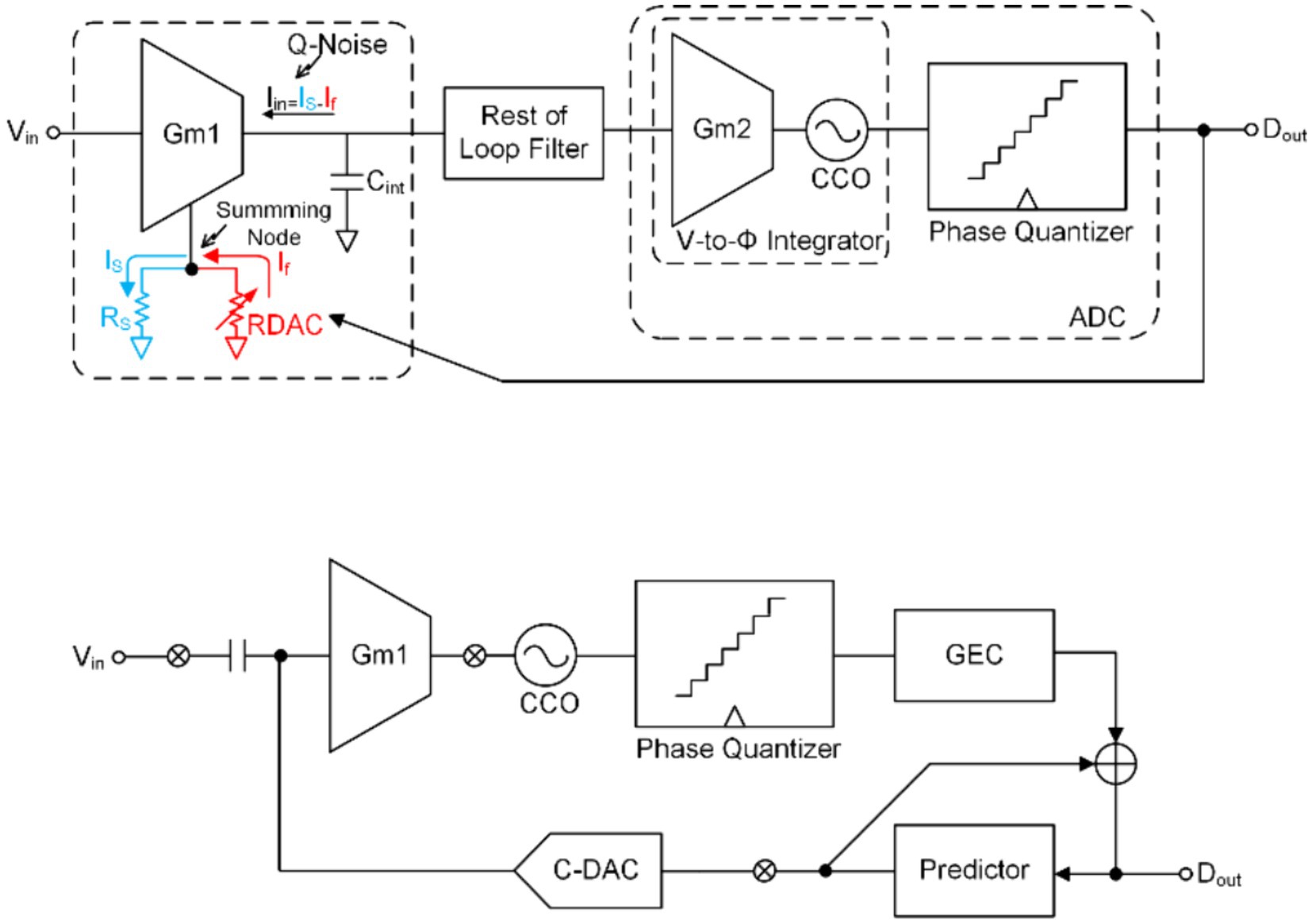

3.9 Direct-conversion topology

All methods described previously require IA combined with ADC to quantify neural signals. With the development of neural signal processing algorithms in recent years, neural signals and artifacts can be distinguished directly from the signals recorded by the neural recording front-end. As a result, direct-conversion topologies were developed to replace the traditional neural recording front-end that combines IA with ADC (Lee et al., 2020). Direct quantification of artifact-containing neural signals requires neural recording front-ends with large DR, linearity, and signal-to-noise-and-distortion ratio (SNDR). Motivated by feedback-based approach published in (Muller et al., 2011; Kassiri et al., 2016), DSM quickly became the preferred structure for direct quantification applications (Jung et al., 2022a,b).

One of the topologies is derived from highly linear DC-coupled based CT-DSM for artifact-tolerant neural recording (Jeon et al., 2019; Lee et al., 2020). The conceptual block diagram of DC-coupled based CT-DSM with the resistive feedback digital-to-analog convertor (RDAC) is shown in Figure 12A. The DC-coupled DSM (Nikas et al., 2019; Moeinfard and Kassiri, 2022) has a higher input impedance than ac-couple DSM with chopper topology (Johnson et al., 2017; Bang et al., 2018; Zhao et al., 2019) and conventional based CT-DSM (Schoofs et al., 2007; Sarhangnejad et al., 2011; Huang et al., 2015) (implementing a summing node at the output of the integrator). The traditional way to improve the linearity of is to achieve it through source degeneration technology (Wattanapanitch et al., 2007), but this will still cause the output of Gm to saturate in the case of a larger input signal. This occurs because the current generated by the source degeneration resistor is much larger than the bias current (or input transistor current) and can only be improved by increasing the resistance of . To address the limitation of source degeneration technology, real-time adjustment of its current variations can be achieved through the integration of a negative feedback loop. In order to improve the linearity of , RDAC and are connected in parallel. In this way, CTDSM can be used to make the current generated by the input signal equal to the feedback current of the RDAC. Due to the feedback-assisted Gm linearization, the magnitude of the maintains within the LSB of feedback DAC current even with a large input voltage, which improves the linearity of the integrator significantly (Lee, C. et al., 2020). A VCO-based integrator and quantizer, implementing with a cell followed by two current-control oscillators (CCOs) is implemented to improve energy and area efficiency.

Figure 12. (A) The block diagram of the DC coupling CT-DMS ADC. (B) The block diagram of a DSM using a time-based quantizer and DPCM.

Another topology applies digital pulse code modulation (DPCM) as a predictor that exploits correlation between adjacent samples of the input signal (Huang and Mercier, 2020, 2021), as shown in Figure 12B. The prediction of DPCM significantly reduces the input signal swing to improve the linearity of and CCO.

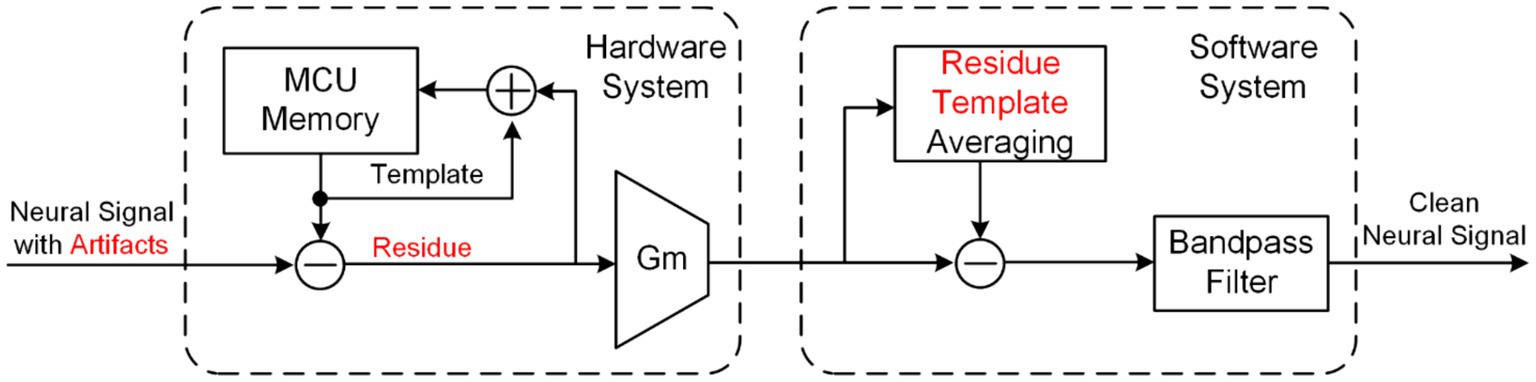

3.10 Artifact template subtraction algorithm

While the aforementioned technologies address artifacts at the hardware system, it should be noted that no hardware system can comprehensively resolve or formulate the theory of large artifact removal in same-electrode stimulation and recording. Additionally, complete hardware systems entail stringent system requirements and pose challenges in adapting to diverse application scenarios. Therefore, post-processing artifact suppression technology is needed to further process the neural signals in software system (or called algorithm) collected by the hardware system.

Template subtraction (Culaclii et al., 2016, 2018; Pérez-Prieto et al., 2019) is a typical technology for eliminating artifacts in software systems, as shown in Figure 13. The neural signal finally output by the software system is obtained by subtracting a template representing the artifact waveform from the neural signal accompanying artifacts collected by the hardware system. The template can be generated by averaging the artifacts, polynomial function-fitting, and filtering based on wavelet methods and Hampel identifiers. The initial template is stored by the iterative hardware loop, then the template is gradually updated with each recorded artifact difference until the template converges in the hardware resolution.

Figure 13. The block diagram of an online artifact cancelation in same-electrode system using combined hardware and software system.

It is important to recognize that if the neural recording front-end becomes saturated, software approach may fail to accurately process the desired neural signals. Hence, the integration of this technology with a hardware system boasting a larger dynamic range, as shown in Figure 13, is imperative to effectively eliminate artifacts, as demonstrated in (Culaclii et al., 2016, 2018).

4 Summary and classification

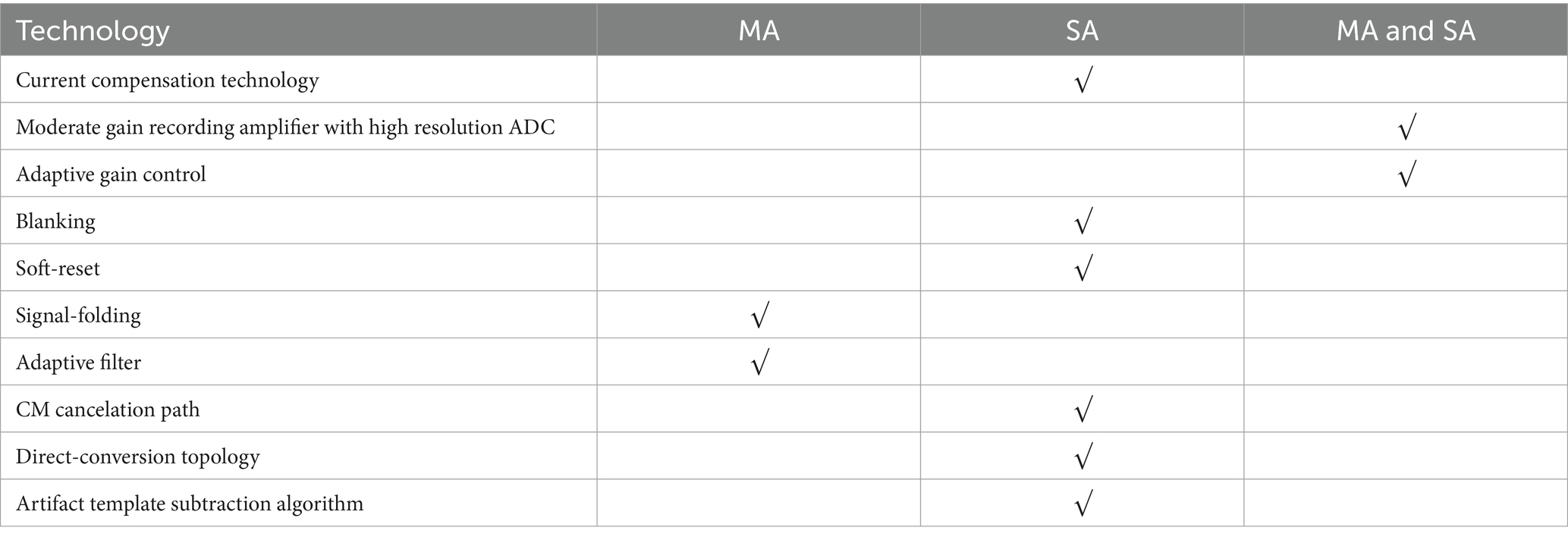

We have categorized all the technologies listed above, some technologies are only applied to MA, some technologies are only applied to SA, and some technologies are applied to both MA and SA, as shown in Table 2.

The previous section listed 10 technologies related to eliminating the impact of artifacts, and most of them have become the core technologies for addressing the closed-loop brain-computer interface artifact problem in recent years. We have selected 7 of the most representative articles in the past few years for comparison (as shown in Table 3). The technologies they apply encompass all the above-mentioned methods for mitigating the impact of artifacts.

Author contributions

WC: Conceptualization, Data curation, Formal analysis, Funding acquisition, Investigation, Methodology, Project administration, Resources, Software, Supervision, Validation, Visualization, Writing – original draft, Writing – review & editing. XL: Data curation, Formal analysis, Funding acquisition, Validation, Writing – review & editing. PW: Data curation, Formal analysis, Methodology, Writing – review & editing. ZC: Funding acquisition, Investigation, Project administration, Writing – review & editing. YC: Conceptualization, Resources, Supervision, Writing – review & editing.

Funding

The author(s) declare that financial support was received for the research, authorship, and/or publication of this article. This work is supported by the Beijing Natural Science Foundation Program under Grant No. 4222062.

Conflict of interest

The authors declare that the research was conducted in the absence of any commercial or financial relationships that could be construed as a potential conflict of interest.

Publisher's note

All claims expressed in this article are solely those of the authors and do not necessarily represent those of their affiliated organizations, or those of the publisher, the editors and the reviewers. Any product that may be evaluated in this article, or claim that may be made by its manufacturer, is not guaranteed or endorsed by the publisher.

References

Bang, J S, Jeon, H, Je, M, and Cho, G. -H., 6.5 μW 92.3 dB-DR biopotential-recording front-end with 360mV pp linear input range. 2018 IEEE symposium on VLSI circuits, (2018): 239–240.

Bi, Z Y, Xie, C X, Zhou, Y X, Wang, HP, Lu, XY, and Wang, ZG, An anti stimulation artifacts and M-waves surface electromyography detector with a short blanking time. 2020 42nd Annual International Conference of the IEEE Engineering in Medicine & Biology Society (EMBC). IEEE, (2020): 4126–4129.

Chandrakumar, H., and Marković, D. (2017a). A high dynamic-range neural recording chopper amplifier for simultaneous neural recording and stimulation. IEEE J. Solid State Circuits 52, 645–656. doi: 10.1109/JSSC.2016.2645611

Chandrakumar, H., and Marković, D. (2017b). An 80-mVpp linear-input range, 1.6-GΩ input impedance, low-power chopper amplifier for closed-loop neural recording that is tolerant to 650-mVpp common-mode interference. IEEE J. Solid State Circuits 52, 1–18. doi: 10.1109/JSSC.2017.2753824

Chandrakumar, H, and Markovic, D. 27.1 a 2.8 μW 80mV pp-linear-input-range 1.6 GΩ-input impedance bio-signal chopper amplifier tolerant to common-mode interference up to 650mV pp. 2017 IEEE International Solid-State Circuits Conference (ISSCC). IEEE, (2017c): 448–449.

Chandrakumar, H., and Marković, D. (2018). A 15.2-ENOB 5-kHz BW 4.5-μW chopped CT ΔΣ-ADC for artifact-tolerant neural recording front ends. IEEE J. Solid State Circuits 53, 3470–3483. doi: 10.1109/JSSC.2018.2876468

Chen, W, Liu, X, Liang, W, Lu, Z., Wan, P., and Chen, Z.. A low-noise neural signal amplifier achieving 1.6 NEF and 2.56 PEF for brain-machine Interface. 2022 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS). IEEE, (2022): 144–148.

Chen, Y., Basu, A., Liu, L., Zou, X., Rajkumar, R., Dawe, G. S., et al. (2014). A digitally assisted, signal folding neural recording amplifier. IEEE Trans. Biomed. Circuits Syst. 8, 528–542. doi: 10.1109/TBCAS.2013.2288680

Culaclii, S., Kim, B., Lo, Y. K., Li, L., and Liu, W. (2018). Online artifact cancelation in same-electrode neural stimulation and recording using a combined hardware and software architecture. IEEE Trans. Biomed. Circuits Syst. 12, 601–613. doi: 10.1109/TBCAS.2018.2816464

Culaclii, S, Kim, B, Lo, Y K, and Liu, W., A hybrid hardware and software approach for cancelling stimulus artifacts during same-electrode neural stimulation and recording. 2016 38th Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBC). IEEE, (2016): 6190–6193.

Dabbaghian, A., and Kassiri, H. (2023). An 8-channel ambulatory EEG recording IC with In-Channel fully-analog real-time motion artifact extraction and removal. IEEE Trans. Biomed Circuits Syst. 17, 999–1009. doi: 10.1109/TBCAS.2023.3289159

Deb, A, Kar, A, and Chandra, M. An efficient minimum mean M-estimate sub-band adaptive active noise cancellation algorithm. TENCON 2014–2014 IEEE Region 10 Conference. IEEE, (2014): 1–6.

Debarros, J, Gaignon, L, He, S, Pogosyan, A, Benjaber, M, Denison, T, et al. Artefact-free recording of local field potentials with simultaneous stimulation for closed-loop deep-brain stimulation. 2020 42nd Annual International Conference of the IEEE Engineering in Medicine & Biology Society (EMBC). IEEE, (2020): 3367–3370.

Debbarma, S., and Bhadra, S. (2022). A flexible wearable Electrooculogram system with motion artifacts sensing and reduction. IEEE Trans Biomed Circuits Syst 16, 324–335. doi: 10.1109/TBCAS.2022.3168236

Delgado-Restituto, M., Rodriguez-Perez, A., Darie, A., Soto-Sanchez, C., Fernandez-Jover, E., and Rodriguez-Vazquez, A. (2017). System-level design of a 64-channel low power neural spike recording sensor. IEEE Trans. Biomed Circuits Syst. 11, 420–433. doi: 10.1109/TBCAS.2016.2618319

Erbsloh, A., Viga, R., Seidl, K., and Kokozinski, R. (2021). Artefact-suppressing analog spike detection circuit for firing-rate measurements in closed-loop retinal neurostimulators. IEEE Sensors J. 22, 11328–11335. doi: 10.1109/JSEN.2021.3133716

Erez, Y., Tischler, H., Moran, A., and Bar-Gad, I. (2010). Generalized framework for stimulus artifact removal. J. Neurosci. Methods 191, 45–59. doi: 10.1016/j.jneumeth.2010.06.005

Fan, Q., Sebastiano, F., Huijsing, J. H., and Makinwa, K. A. A. (2011). A 1.8 μW 60nV Hz Capacitively-coupled chopper instrumentation amplifier in 65 nm CMOS for wireless sensor nodes. IEEE J. Solid State Circuits 46, 1534–1543. doi: 10.1109/JSSC.2011.2143610

Guglielmi, E., Toso, F., Zanetto, F., Sciortino, G., Mesri, A., Sampietro, M., et al. (2020). High-value tunable pseudo-resistors design. IEEE J. Solid State Circuits 55, 2094–2105. doi: 10.1109/JSSC.2020.2973639

Harrison, R. R., and Charles, C. (2003). A low-power low-noise CMOS amplifier for neural recording applications. IEEE J. Solid State Circuits 38, 958–965. doi: 10.1109/JSSC.2003.811979

Huang, C. W., Lai, C. K., Hung, C. C., Wu, C. Y., and Ker, M. D. (2023). A CMOS synchronized sample-and-hold artifact blanking analog front-end local field potential acquisition unit with 3.6-V stimulation artifact tolerance and monopolar electrode-tissue impedance measurement circuit for closed-loop deep brain stimulation SoCs. IEEE Trans. Circuits Syst. 70, 2257–2270. doi: 10.1109/TCSI.2023.3254891

Huang, C W, Wang, J J, Hung, C C, and Wu, C. Y. Design of CMOS analog front-end electroencephalography (EEG) amplifier with±1-V common-mode and±10-mV differential-mode artifact removal. 2022 IEEE Biomedical Circuits and Systems Conference (BioCAS). IEEE, (2022): 714–717.

Huang, J., and Mercier, P. P. (2020). A 112-dB SFDR 89-dB SNDR VCO-based sensor front-end enabled by background-calibrated differential pulse code modulation. IEEE J. Solid State Circuits 56, 1046–1057. doi: 10.1109/JSSC.2020.3037833

Huang, J., and Mercier, P. P. (2021). A 178.9-dB FoM 128-dB SFDR VCO-based AFE for ExG readouts with a calibration-free differential pulse code modulation technique. IEEE J. Solid State Circuits 56, 3236–3246. doi: 10.1109/JSSC.2021.3112635

Huang, J., Yang, S., and Yuan, J. (2015). A 75 dB SNDR 10-MHz signal bandwidth gm-C-based sigma-delta modulator with a nonlinear feedback compensation technique. IEEE Trans. Circuits Syst. 62, 2216–2226. doi: 10.1109/TCSI.2015.2452333

Islam, M. K., Rastegarnia, A., Nguyen, A. T., and Yang, Z. (2014). Artifact characterization and removal for in vivo neural recording. J. Neurosci. Methods 226, 110–123. doi: 10.1016/j.jneumeth.2014.01.027

Islam, M K, Tuan, N A, Zhou, Y, and Yang, Z.. Analysis and processing of in-vivo neural signal for artifact detection and removal. 2012 5th International Conference on BioMedical Engineering and Informatics. IEEE, (2012): 437–442.

Jeon, H., Bang, J. S., Jung, Y., Choi, I., and Je, M. (2019). A high DR, DC-coupled, time-based neural-recording IC with degeneration R-DAC for bidirectional neural interface. IEEE J. Solid State Circuits 54, 2658–2670. doi: 10.1109/JSSC.2019.2930903

Johnson, B C, Gambini, S, Izyumin, I, Gambini, Simone, Izyumin, Igor, Moin, Ali, et al. An implantable 700μW 64-channel neuromodulation IC for simultaneous recording and stimulation with rapid artifact recovery. 2017 symposium on VLSI circuits. IEEE, (2017): C48–C49.

Jung, Y., Kweon, S. J., Jeon, H., Choi, I., Koo, J., Kim, M. K., et al. (2022b). A wide-dynamic-range neural-recording ic with automatic-gain-controlled AFE and CT dynamic-zoom ΔΣ ADC for saturation-free closed-loop neural interfaces. IEEE J. Solid State Circuits 57, 3071–3082. doi: 10.1109/JSSC.2022.3188626

Jung, Y, Kweon, S J, Jeon, H, Lee, Taeju, Choi, Injun, Jeong, Kyeongwon, et al. A 99.5 dB-DR 5kHz-BW closed-loop neural-recording IC based on continuous-time dynamic-zoom ΔΣ ADC with automatic AFE-gain control. 2021 IEEE Asian Solid-State Circuits Conference (A-SSCC), (2021): 1–3.

Jung, Y., Kweon, S. J., Lee, T., Jeong, K., Ha, S., and Je, M. (2022a). Dynamic-range-enhancement techniques for artifact-tolerant biopotential-acquisition ics. IEEE Trans Circuits Syst II Express Briefs 69, 3090–3095. doi: 10.1109/TCSII.2022.3176272

Kassiri, H., Bagheri, A., Soltani, N., Abdelhalim, K., Jafari, H. M., Salam, M. T., et al. (2016). Battery-less tri-band-radio neuro-monitor and responsive neurostimulator for diagnostics and treatment of neurological disorders. IEEE J. Solid State Circuits 51, 1274–1289. doi: 10.1109/JSSC.2016.2528999

Lee, C., Jeon, T., Jang, M., Park, S., Kim, J., Lim, J., et al. (2020). A 6.5-μW 10-kHz BW 80.4-dB SNDR G m-C-based CT ∆Σ modulator with a feedback-assisted G m linearization for artifact-tolerant neural recording. IEEE J. Solid State Circuits 55, 2889–2901. doi: 10.1109/JSSC.2020.3018478

Li, J., Chen, W., Liu, X., Wan, P., and Chen, Z. (2023). A 4-channel neural stimulation IC design with charge balancing and multiple current output modes. IEEE Trans. Biomed. Circuits Syst. 17, 1037–1049. doi: 10.1109/TBCAS.2023.3316969

Liu, X, Yao, L, Li, P, Liu, Lei, Zou, Xiaodan, Je, Minkyu, et al. An artifact-suppressed stimulator for simultaneous neural recording and stimulation systems. 2017 39th Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBC). IEEE, (2017): 2118–2121.

Liu, X., Zhang, M., Richardson, A. G., Lucas, T. H., and van der Spiegel, J. (2016). Design of a closed-loop, bidirectional brain machine interface system with energy efficient neural feature extraction and PID control. IEEE Trans Biomed Circuits Syst. 11, 729–742. doi: 10.1109/TBCAS.2016.2622738

Liu, Y., Urso, A., Martins da Ponte, R., Costa, T., Valente, V., Giagka, V., et al. (2020). Bidirectional bioelectronic interfaces: system design and circuit implications. IEEE Solid-State Circuits Magazine 12, 30–46. doi: 10.1109/MSSC.2020.2987506

McFarland, D. J., Daly, J., Boulay, C., and Parvaz, M. A. (2017). Therapeutic applications of BCI technologies. Brain-Comput. Interfaces 4, 37–52. doi: 10.1080/2326263X.2017.1307625

Moeinfard, T, and Kassiri, H. A 200GΩ-Z IN,< 0.2%-THD CT-ΔΣ-based ADC-direct artifact-tolerant neural recording circuit. 2022 IEEE International Symposium on Circuits and Systems (ISCAS). IEEE, (2022): 1901–1905.

Mondal, S, and Hall, D A. An ECG chopper amplifier achieving 0.92 NEF and 0.85 PEF with AC-coupled inverter-stacking for noise efficiency enhancement. 2017 IEEE International Symposium on Circuits and Systems (ISCAS). IEEE, (2017): 1–4.

Muller, R., Gambini, S., and Rabaey, J. M. (2011). A 0.013 mm2, 5 μW, DC-coupled neural signal acquisition IC with 0.5 V supply. IEEE J. Solid State Circuits 47, 232–243. doi: 10.1109/JSSC.2011.2163552

Nikas, A., Jambunathan, S., Klein, L., Voelker, M., and Ortmanns, M. (2019). A continuous-time delta-sigma modulator using a modified instrumentation amplifier and current reuse DAC for neural recording. IEEE J. Solid State Circuits 54, 2879–2891. doi: 10.1109/JSSC.2019.2931811

Oh, W., Bakkaloglu, B., Wang, C., and Hoon, S. K. (2008). A CMOS low noise, chopper stabilized low-dropout regulator with current-mode feedback error amplifier. IEEE Trans Circuits Syst I 55, 3006–3015. doi: 10.1109/TCSI.2008.923278

Pérez-Prieto, N, Delgado-Restituto, M, and Rodríguez-Vázquez, Á. Artifact-aware analogue/mixed-signal front-ends for neural recording applications. 2019 IEEE International Symposium on Circuits and Systems (ISCAS). IEEE, (2019): 1–5.

Pham, X. T., Tran, X. P., Nguyen, K. V., Le, V. T., Pham, D. P., and Hoang, M. K. (2022). A 1.9 μW 127 nVHz bio chopper amplifier using a noise-efficient common mode cancelation loop. 2022 international conference on advanced Technologies for Communications (ATC). IEEE, 116–120. doi: 10.1109/ISSCC.2016.7417923

Pu, H., Malekzadeh-Arasteh, O., Danesh, A. R., Nenadic, Z., do, A. H., and Heydari, P. (2021). A CMOS dual-mode brain-computer interface chipset with 2-mV precision time-based charge balancing and stimulation-side artifact suppression. IEEE J. Solid State Circuits 57, 1824–1840. doi: 10.1109/JSSC.2021.3108578

Qiu, Z., Nguyen, A. T., Su, K., Yang, Z., and Xu, J. (2023). A high precision, wide dynamic range closed-loop neuromodulation IC with rapid stimulation artifact recovery. IEEE Trans. Biomed. Circuits Syst. 18, 274–287. doi: 10.1109/TBCAS.2023.3321295

Samiei, A., and Hashemi, H. (2021). A bidirectional neural interface SoC with adaptive IIR stimulation artifact cancelers. IEEE J. Solid State Circuits 56, 2142–2157. doi: 10.1109/JSSC.2021.3056040

Sarhangnejad, N, Wu, R, Chae, Y, and Makinwa, K. A. A., A continuous-time ΣΔ modulator with a gm-C input stage, 120-dB CMRR and −87 dB THD. IEEE Asian Solid-State Circuits Conference 2011. IEEE, (2011): 245–248.

Schoofs, R., Steyaert, M. S. J., and Sansen, W. M. C. (2007). A design-optimized continuous-time delta–sigma ADC for WLAN applications. IEEE Trans. Circuits Syst. 54, 209–217. doi: 10.1109/TCSI.2006.887455

Shadmani, A., Viswam, V., Chen, Y., Bounik, R., Dragas, J., Radivojevic, M., et al. (2019). Stimulation and artifact-suppression techniques for in vitro high-density microelectrode array systems. IEEE Trans. Biomed. Eng. 66, 2481–2490. doi: 10.1109/TBME.2018.2890530

Sharma, K., Goyal, L., and Gupta, L. (2016). Implementation of tunable and non tunable Pseudo-resistors using 0.18 μm technology. Int. J. Comp. App. 975:8887.

Sugiyama, A, Miyahara, R, and Kato, M. An adaptive noise canceller with adaptive delay compensation for a distant noise source. 2011 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP). IEEE, (2011): 265–268.

van Helleputte, N., Konijnenburg, M., Pettine, J., Jee, D. W., Kim, H., Morgado, A., et al. (2014). A 345 μW multi-sensor biomedical SoC with bio-impedance, 3-channel ECG, motion artifact reduction, and integrated DSP. IEEE J. Solid State Circuits 50, 230–244. doi: 10.1109/JSSC.2014.2359962

Verma, N., Shoeb, A., Bohorquez, J., Dawson, J., Guttag, J., and Chandrakasan, A. P. (2010). A micro-power EEG acquisition SoC with integrated feature extraction processor for a chronic seizure detection system. IEEE J. Solid State Circuits 45, 804–816. doi: 10.1109/JSSC.2010.2042245

Viswam, V, Chen, Y, Shadmani, A, Dragas, J, Bounik, R, Milos, R, et al. 2048 action potential recording channels with 2.4 μVrms noise and stimulation artifact suppression. 2016 IEEE Biomedical Circuits and Systems Conference (BioCAS). IEEE, (2016): 136–139.

Wang, Y., Luo, H., Chen, Y., Jiao, Z., Sun, Q., Dong, L., et al. (2021). A closed-loop neuromodulation chipset with 2-level classification achieving 1.5-Vpp CM interference tolerance, 35-dB stimulation artifact rejection in 0.5 ms and 97.8%-sensitivity seizure detection. IEEE Trans. Biomed. Circuits Syst. 15, 802–819. doi: 10.1109/TBCAS.2021.3102261

Wattanapanitch, W., Fee, M., and Sarpeshkar, R. (2007). An energy-efficient micropower neural recording amplifier. IEEE Trans. Biomed. Circuits Syst 1, 136–147. doi: 10.1109/TBCAS.2007.907868

Xu, J., Nguyen, A. T., Zhao, W., Guo, H., Wu, T., Wiggins, H., et al. (2018). A low-noise, wireless, frequency-shaping neural recorder. IEEE J. Emerg.Select.Topics Circuits Syst. 8, 187–200. doi: 10.1109/JETCAS.2018.2812104

Zhang, J., Zhang, H., Sun, Q., and Zhang, R. (2018). A low-noise, low-power amplifier with current-reused OTA for ECG recordings. IEEE Trans. Biomed. Circuits Syst. 12, 700–708. doi: 10.1109/TBCAS.2018.2819207

Zhao, W., Li, S., Xu, B., Yang, X., Tang, X., Shen, L., et al. (2019). A 0.025-mm 2 0.8-V 78.5-dB SNDR VCO-based sensor readout circuit in a hybrid PLL-ΔΣM structure. IEEE J. Solid State Circuits 55, 666–679. doi: 10.1109/JSSC.2019.2959479

Zou, X., Liu, L., Cheong, J. H., Yao, L., Li, P., Cheng, M. Y., et al. (2013). A 100-channel 1-mW implantable neural recording IC. IEEE Trans. Circuits Syst. 60, 2584–2596. doi: 10.1109/TCSI.2013.2249175

Keywords: biomedical, motion artifact, stimulation artifact, neural recording, closed-loop brain-machine interface

Citation: Chen W, Liu X, Wan P, Chen Z and Chen Y (2024) Anti-artifacts techniques for neural recording front-ends in closed-loop brain-machine interface ICs. Front. Neurosci. 18:1393206. doi: 10.3389/fnins.2024.1393206

Edited by:

S. Abdollah Mirbozorgi, University of Alabama at Birmingham, United StatesReviewed by:

Fernando Silveira, Facultad de Ingeniería, Universidad de la República, UruguayZhen Yuan, University of Macau, China

Copyright © 2024 Chen, Liu, Wan, Chen and Chen. This is an open-access article distributed under the terms of the Creative Commons Attribution License (CC BY). The use, distribution or reproduction in other forums is permitted, provided the original author(s) and the copyright owner(s) are credited and that the original publication in this journal is cited, in accordance with accepted academic practice. No use, distribution or reproduction is permitted which does not comply with these terms.

*Correspondence: Xu Liu, bGl1eHUxNkBianV0LmVkdS5jbg==; Yi Chen, Y2hlbnlpQGJhZWMub3JnLmNu

Weijian Chen

Weijian Chen Xu Liu

Xu Liu Peiyuan Wan1

Peiyuan Wan1