### **Review Article**

# How to make lithography patterns print: the role of OPC and pattern layout

Abstract: This paper will review some of the methods that have been devised to bring lithography-generated patterns as close to the desired target patterns as possible, while making them also robust against inevitable deviations from the ideal conditions during the printing process. Optical proximity correction (OPC) is the first step in this process. Various ways have been developed for efficient creation of accurate process window aware OPC models. Also, the use of the actual OPC step, to transform the target patterns into actual lithography mask patterns has seen significant progress. A computational verification step then checks whether the predicted pattern shapes meet the quality requirements and identifies any residual failures or weak patterns ('hotspots'). Once the mask is available, a second verification step, now looking at patterns on printed wafers, is performed to make sure that all critical patterns print to within the requested tolerances. Each of the steps in this flow can - and usually does lead to corrective iterations to one of the previous steps. As the task of ensuring sufficient process margin is gradually becoming more difficult, with the ever decreasing pattern sizes, constraints are being increasingly defined on the type of patterns that can be allowed in the target layout itself (design restrictions), leading to a tendency toward more regular designs, an evolution that needs to be facilitated by the patterning technology and materials used. So the problem of ensuring good printability now also involves both layout and technology, and we will look into this aspect of the optimization problem as well.

**Keywords:** DTCO; geometrical layout restrictions; OPC; optical lithography; unidirectional layouts.

DOI 10.1515/aot-2015-0023

Received March 15, 2015; accepted April 14, 2015; previously published online May 20, 2015

www.degruyter.com/aot © 2015 THOSS Media and De Gruyter

### **1** Introduction

Semiconductor devices are built as stacks of patterned layers, where the lithography step is the one creating the basic patterning of each of the layers. This is done by transferring patterns from a mask to a photosensitive layer (resist) that has been spun on the wafer, using an optical projection system. The resist pattern is then subsequently transferred into the underlying layers by an etch or an implantation step [1]. Repeating this cycle, layer by layer, creates a three-dimensional stack that eventually becomes the semiconductor device.

Whether or how well this device will work, depends (among others) on the quality of the patterns in each of the process layers, i.e., how close they are to the intended or target pattern, even when the printing condition deviates from the ideal conditions, e.g., because of (inevitable) errors in the focus or dose of the scanner or errors in the mask pattern. Therefore, methods and tools of increasing sophistication have been developed over the past decades to optimize both pattern fidelity and robustness, as much as possible.

Among these, optical proximity correction (OPC) plays a key role. The need for OPC is caused by the fact that the projection lens in the lithographic exposure tool (the 'scanner') – due to its finite size (NA) – cannot recombine all the diffracted light into the reconstructed image at the wafer side [1, 2]. This implies that this image will not be identical to the pattern on the mask. This image deviation becomes more important with decreasing target-pattern size, but it is also highly pattern dependent. OPC uses a combined optics-resist model (and if desired also etch model) to correct for this proximity effect, by converting the pattern on the mask from the target pattern into a different one, such that what is printed on the wafer will, in fact, approach the target pattern as closely as possible [3, 4].

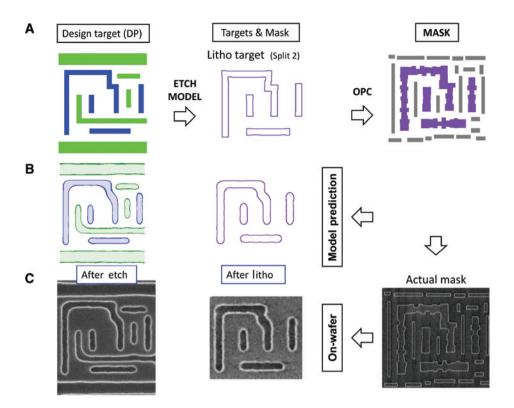

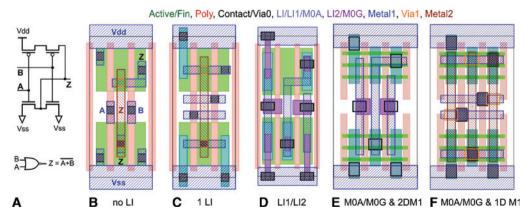

Figure 1A illustrates the basic OPC concept for a small example clip of a 20-nm logic node (N20) Metal1 layer, that is already split into two separate layers or 'colors' (double patterning). The etch model converts the design

<sup>\*</sup>Corresponding author: Peter De Bisschop, Advanced Lithography Department, IMEC, Kapeldreef 75, B-3001 Leuven, Belgium, e-mail: peter.debisschop@imec.be

**Figure 1:** Illustrating OPC for a double-patterning N20 Metal1 example (NTD resist process). (A) OPCed mask pattern generation; the gray shapes are the SRAFs. (B) Predicted pattern after litho, i.e., in resist and after etch, and (C) actual wafer pattern after litho and etch. Also shown is a SEM image of the OPCed mask pattern itself.

target pattern into the litho target pattern, and the opticsresist model, then further transforms it to the pattern that is actually placed on the mask. For critical layers, this OPCed pattern also contains subresolution assist features, or SRAFs (gray polygons): these are not supposed to print, but help make the printing of the final pattern more robust against certain process variations [1]. Figure 1B and C illustrate the expected pattern (as predicted by the OPC software) and the actually observed pattern of the wafer, after the litho and the litho and etch step, respectively. (The etch step in this example is also used to trim down the dimensions of the litho pattern.)

Several electronic design automation (EDA) companies – e.g., Mentor Graphics, Synopsys, Brion (currently an ASML company), and Cadence – offer software packages that are capable of making such OPC corrections for a complete mask within an acceptable time.

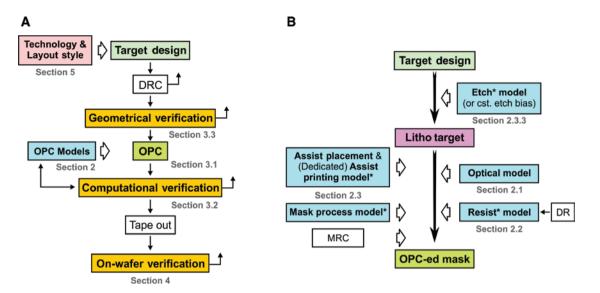

The software that makes such an OPC correction to the design pattern is of course based on models that describe how a specific pattern on the mask is expected to print on the wafer. The success of the OPC correction is then evidently related to the accuracy of these models. In Section 2, we will discuss how such OPC models are built and how their quality can be evaluated. Application of these models in the actual OPC mask correction – an art in itself – and the computational verification step that is done immediately after that will be discussed in Section 3. Once the masks are available, an on-wafer verification of the pattern quality and robustness is done. This step will be discussed in Section 4. In the final section of this paper, we will show how geometrical simplifications in the allowed design patterns are becoming an important additional weapon in the battle for printable patterns. Figure 2 shows the flow from the target layout to the on-wafer patterning and refers each of these steps to the various (sub-) sections of this paper.

Before we start, the following remark must be made. The subject of 'optimization of lithographic printability' is, in fact, a very broad one, and covering all of it in a single paper is not feasible. This complete optimization flow includes things like choosing the resist and process stack, defining the stepper conditions (including the scanner source shape), defining an antireflection strategy, etc. [1]. This paper steps into the larger flow at the point where all these 'operational conditions' have been fixed and when at least some basic ground rules for the process layer under consideration are known. This paper will focus on today's state of the art, while also looking

**Figure 2:** Simplified schematic of the steps that need to be taken to take the target layouts to robustly printing wafer patterns, making also reference to the sections in this paper. (A) General flow; (B) models involved in the OPC step (models marked with an asterisk need to be calibrated on wafer data). For most steps in the flow, iterations to previous steps usually take place (symbolized by the upward pointing arrows) before all patterns in the chip print to within the required quality specifications.

back into recent (published) history, to see how we got where we are today.

The Appendix contains a summary of most of the abbreviations used in this paper.

### 2 OPC models

The software that makes OPC corrections on the design pattern is based on models that describe how a specific pattern on the mask is expected to print on the wafer. In this section, we will look into these models, see how they are built (calibrated) and point out some of the mechanisms that could/should be included. The purpose is to review where potential sources of remaining inaccuracies or error could be, as these will transfer into inaccuracies in the OPC corrections applied and, hence, the quality of the printed wafer patterns.

Lithography models consist of two – and if we include also etch, of three – major steps [1]:

- 1. In the first step, the 'optical image' is calculated, using an 'Optical Model'. The term 'optical image' refers to the light-intensity distribution that is created by the projection lens inside the volume of the resist film, I(x, y, z).

- 2. The second step calculates how this optical image eventually gives rise to a resist pattern, after the bake/ development/rinse step. This calculation includes

mechanisms that describe how light interacts with the resist, interactions between the different resist components (such as acid-catalyzed deprotection, acid-quencher interactions, acid and quencher diffusion and development). At the end of this step, the variations in the optical image intensity have been converted into areas where the resist has been removed by the developer and areas where resist still remains. We will refer to models behind this step in the calculation as the 'Resist Model'.

3. In the final patterning step, the resist pattern is transferred into some material layer (stack) below, often using some dry-etch step. This step is then described by an 'Etch Model', i.e., some mathematical formalism that tells whether and how the etch process further changes the resist pattern.

We will discuss each of these separately.

### 2.1 Optical model

It is, in principle, possible to calculate the image intensity distribution inside the resist film very accurately (assuming that all the optical properties of the projection system are known, which in general is, to a large extent, the case), though not at an affordable price if this needs to be done for large areas, such as the full mask. OPC, as in the case of any complicated calculation, must find a balance between the conflicting requirements of accuracy and speed. Simulators referred to as 'rigorous lithography simulators', such as Sentaurus Lithography (or S-Litho, from Synopsys, Mountain View, CA, USA), Prolith (from KLA-Tencor, Milpitas, CA, USA), Hyperlith (Panoramic Technology Inc., USA) or Dr. LiTHO (Fraunhofer IISB, Erlangen, Germany), simulate the lithographic process for a very small mask area only (typically a few µm by a few µm at the most) and can, therefore, go for the highest accuracy while keeping the calculation time within reasonable limits. The much larger mask area that OPC simulators need to cover necessitates approximations in order to keep simulation times realistic. The first simplification that is being made is that the image intensity inside the resist is only calculated (at least in general) in a single xy plane (parallel to the wafer surface), at some selected z-position  $(z_0)$ , instead of in the entire volume of the resist film. It is from this two-dimensional image intensity, I(x, y), that the essentially three-dimensional developed resist pattern will be deduced with the Resist Model. We will come back to this simplification later.

When practical OPC came into use in the early 1990s, this intensity function I(x, y) was calculated with what is referred to as the 'scalar approach', which means that light was treated as a scalar wave, ignoring its polarization, i.e., its vector-wave character. Also, the mask was treated as infinitely thin, so that it can be described by a simple, binary mask function, M(x, y), that has values of either 0 or 1 depending on whether or not the mask is transmitting at position (x, y). This assumption is referred to as the 'Kirchhoff' or 'Thin Mask' approximation (TMA). An equation for I(x, y) under these assumptions has essentially been known since the 1950s and has been described in several publications, e.g., [1, 2]. Approaches to efficiently apply this formalism to entire mask areas express this intensity function essentially as [1, 4, 5]:

$$I(\mathbf{x}, \mathbf{y}; \mathbf{z}_0) \approx \sum_n c_n |\mathbf{M}(\mathbf{x}, \mathbf{y}) \otimes \phi_n(\mathbf{x}, \mathbf{y}; \mathbf{z}_0)|^2$$

(1)

i.e., as a sum of convolutions of the mask function M(x, y) with so-called 'optical kernel' functions,  $\phi_n$ . It is important to note that both these kernels as well as the coefficients  $c_n$  are determined directly from optical properties of the illuminator, the mask, the lens, and the resist, so that Eq. (1) does not stand for a fitting operation. Also, the  $c_n$  coefficients decrease with increasing n, such that the sum can be truncated at some convenient maximum value of n. As the kernels do not depend on the mask pattern (i.e., on M), they can be calculated once (for the optical settings used) and then applied to the intensity calculation at positions (x, y) covering the entire mask. This is what makes this process so efficient.

In its use for doing OPC for advanced-node masks today, Eq. (1) has the following mechanisms built into  $c_n$  and  $\phi_n$ :

- 1. The so-called *'thin-film' effects:* light reflections at effectively every interface between the different layers of the wafer-resist stack modify the intensity inside the resist film, creating a standing wave in this layer [6].

- 2. The ability to include lens aberrations - which includes an offset from the best-focus plane (a 'defocus'), or lens apodization - if desired. Especially, the ability to include defocus as well as dose as variables into the model is important. This has led to the socalled process window (PW) models, i.e., models that can also predict how mask patterns will print in offnominal focus-dose conditions. Such PW models are being used today not only to print the wafer patterns close to the design target when the scanner is operating at its optimum (nominal) focus and dose setting, but also to minimize the variation of the printed patterns if some (unwanted but inevitable) focus or dose errors occur. This approach has been called process window OPC or PWOPC see, e.g., Ref [7]).

- 3. The use of a 'vector model' [8, 9], which is essential when applying Eq. (1) to lenses with the large numerical apertures (NA) that are common today, for which the scalar (or paraxial) approximation is not valid any more. Such a vector model takes the polarized nature of light into account. Today, scanners used to print the critical layers of the advanced nodes are all high-NA systems, so this vector approach has become standard.

There are, however, a number of mechanisms that are not included in the optical model as we have described it here so far, some of which are considered by many to be equally important as the ones we just highlighted. Today's OPC software packages have been or are being extended with advanced options to also include these additional effects. We will now briefly discuss the more important ones.

### 2.1.1 Mask topography or mask-3D (M3D) effects

The absorption layers on the masks used in lithography are thin (a few tens of nm) but not infinitely thin, so the Kirchhoff (or Thin-Mask) approximation that diffraction effects that occur at mask level can be calculated simply as the Fourier transform of M(x, y), is not exact. It has become clear that this approximation is often not justified when applied to the type of mask structures that are being used today, and it is now considered by many as essential to include M3D effects in advanced OPC calculations. Since the early years 2000, EDA companies started working out approximate ways to include M3D effects in their OPC packages. Although this task is now largely completed, it has proven to be a nontrivial one.

M3D effects were first studied in the context of what we previously already called 'rigorous lithography simulators' (e.g., S-Litho or Prolith): including M3D effects in a fully correct way essentially requires solving the Maxwell equations which is slow, but can be done with appropriate mathematical techniques if the mask area for which the calculation needs to be done is small. Examples of such studies, with some discussion on the methods used, can be found, e.g., in references [10-12]. From the combined literature on this topic, it has become clear that M3D effects induce pattern-specific CD changes (and, hence, affect the proximity behavior) as well as changes in the through-focus behavior (Bossung distortions and/or bestfocus shifts) of certain structures. To make matters more complicated, it was also found that a correct description of M3D effects requires that the Maxwell equations need to be solved separately for light incident on the mask at different angles of incidence [12], as opposed to assuming that the amplitudes and phases of the diffracted light are independent of the incident angle (something which has been called the 'no-Hopkins' vs. the 'Hopkins' approach), when solving the Maxwell equations.

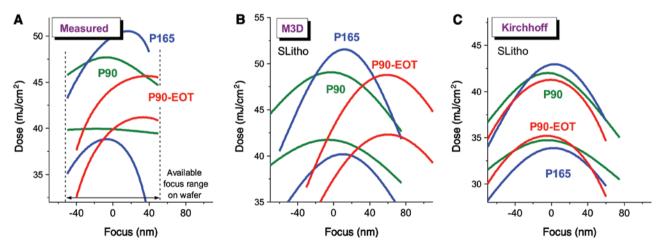

Apart from having an impact on the proximity behavior, itself, M3D effects are also relevant because of the best-focus shifts they induce on some structures. We illustrate this in Figure 3 with the example of three structures we used in the OPC calibration/verification data set for our 20-nm node Metal1 OPC model.

Let us now return to OPC intensity simulations and see how EDA companies have tried to implement M3D effects. One key point to realize is that rigorously solving the Maxwell equations cannot be done on the scale of an entire mask, which means that approximate methods had to be developed that are fast enough to permit full-mask application. It seems that one of the first breakthroughs in efficient M3D calculations was an approximate treatment called the 'domain decomposition method' or DDM [13], later extended to take into account the 'non-Hopkins' oblique incidence effect [14]. Other EDA companies have developed their own approach to solving the M3D puzzle; see, e.g., references [15-18]. A more recent extension of the DDM approach is described in references [19, 20]: DDM essentially treats the impact of topography edges on the mask as independent from each other, but this is an approximation that starts to become invalid as the distance between these edges gradually becomes smaller with decreasing target sizes.

Owing to a lack of published details on each of these implementations, potential differences between the EDA M3D models are difficult to assess. Also, no benchmarking

**Figure 3:** Illustration of the M3D effect on the Process Window of three structures: a 90-nm and 165-nm pitch trench case and a small-gap End-of-Trench (EOT) structure in a 90-nm trench array. (A) Measured from our 20-nm Metal1 OPC model calibration data set, (B) and (C) S-Litho simulated (using an NTD resist model), with a M3D and Thin-mask ('Kirchhoff') model, respectively. The (qualitative) agreement between (A) and (B) shows that M3D effects contribute to the observed best-focus shift. Especially, the EOT case is affected. Note, however, that the amount of focus shift decreases if either the trench pitch or the EOT gap size increases. In our actual 20-nm M1 Logic-cell block, the M3D impact on best focus was much smaller than in the examples shown in this figure. (We allowed the 90-nm pitch in our N20 design rules, but in the double-patterning split Logic patterns, it does not occur). The small best-focus differences in the Kirchhoff case are due to resist effects.

has been published, and their performance cannot be compared. But most of the publications cited report improvements in OPC model quality when M3D models are used, so the current methods have proven the potential to provide benefit. Most important is the ability to account for M3D-induced modifications of the throughfocus behavior of certain structures (e.g., focus shifts) [16, 20, 21], as this is a purely optical effect that should not become 'absorbed' into the parameters of the resist model. Because of the growing importance of these M3D effects, we expect to see further development and validation in the coming years.

### 2.1.2 Mask process corrections (MPC)

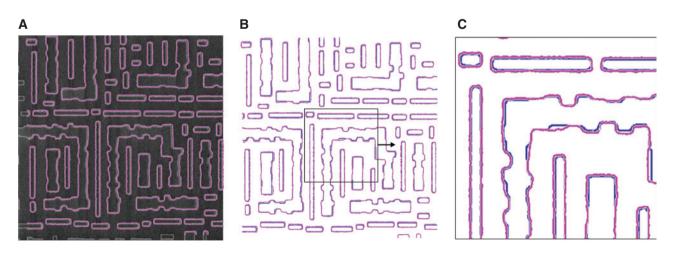

The patterns on real masks, of course, always deviate to some extent from the intended pattern (see the example in Figure 4). A mask has errors, and these will affect the patterns that are printed with them. Mask errors range from global mean-to-target (MTT) deviations, corner rounding, mask-proximity effects, over-etch depth variations, across-mask non-uniformities, etc. An early example of the impact of mask errors and a recent review of the various mask errors that are relevant for OPC can be found in references [22, 23], respectively.

If these mask error effects are constant for a given mask process, and if they can be modeled into what is called a 'mask-process model', it is possible to take them into account during the OPC phase of masks that will be generated later with the same mask process, i.e., it is possible to correct for these errors or at least take them into

account during the OPC process. Mask errors then need to be first measured from a test mask, from which a correction model can be derived for that specific mask process. This means that the ideal mask function, M(x, y), in Eq. (1) is replaced during OPC by a corrected mask function, let us call it M<sub>corr</sub>(x, y), that is closer to what the actual mask will look like. The generation of this corrected mask function can be done in different ways. An overall MTT deviation (or global mask bias) or corner rounding that is constant for all corners can be implemented by a simple operation on M that requires only a few variables as input. These variables can be obtained from a few measurements on a mask made previously with the same process and does not require any extensive mask model building. Figure 4 illustrates this basic concept with a simple example. It shows a mask SEM image and a mask contour that was derived from this image. This contour is then compared (overlayed) with a mask shape that was obtained from a simple bias- and corner-rounding operation on the ideal OPCed shape. Although there are some differences with the measured shape, this simple mask model is clearly already a step in the right direction.

Compensating for more complicated effects, requires a more sophisticated approach that is based on more extensive mask measurements. Depending on which effects one wants to correct for, a set of measured mask error data,  $\Delta CD_{M}$ , will be fitted to a model. A number of model functions that have been mentioned in the literature [24, 25] could be combined into the following equation

$$\Delta CD_{M}(x, y) \approx \Sigma_{i}a_{i}M(x, y) \otimes K_{i}^{S}(x, y) + \Sigma_{i}b_{i}D(x, y) \otimes K_{i}^{L}(x, y) + P(x, y) + MTT$$

(2)

**Figure 4:** (A) Actual mask SEM image of the OPCed pattern shown in Figure 1, together with a mask-edge contour (pink) derived from it. (B) and (C) This measured contour is compared to a simple model shape (blue) obtained by applying a global bias and corner rounding on the ideal after-OPC shape shown in Figure 1.

The first term represents 'short range' mask effects, as a sum of convolutions of M with a set of kernels that are assumed to describe these effects. The second term represents 'long-range' effects, having their own kernels that are now convoluted not with M but with a more coarse 'mask-density function' (D) that is derived from M. The third term is some appropriate polynomial that represents the overall (i.e., structure independent) across-mask nonuniformity. An important difference with Eq. (1) is that, here, the kernel functions K<sup>s</sup>, K<sup>L</sup>, and P are not derived from some rigorous theory but have been adopted by the EDA because they were found to fit well with experimental data in earlier exercises. The parameters (a, and b,) in the two sum terms as well as in the polynomial now have to be fitted to experimental  $\Delta CD_{M}$  data. Once the mask process model of Eq. (2) - or a similar expression - has been experimentally determined, it can be used to predict what the actual mask contour will look like for a given intended M(x, y), and this function can then be used instead of M in the calculation of the optical images of Eq. (1).

It does not seem as if the MPC correction approach as sketched in this section is standard practice today. In the past, mask errors were usually not taken into account explicitly in OPC model building, which means that they were effectively 'absorbed' into the fitted parameters of the resist model. Although this approach seems to have worked well for 'older' technology nodes, incorporating mask effects into the resist model must lead to some error, and with diminishing process margins everywhere, it can be expected that some sort of MPC approach will become increasingly beneficial.

### 2.1.3 Resist 3D

Traditional OPC modeling considers the image intensity in a single xy-plane only (see Eq. 1) and then uses its resist model to derive the printed resist pattern as a contour in that plane. We will refer to this as the 'Resist-2D' (or R2D) approach. But in reality, resist patterns are threedimensional shaped, with (structure dependent) effects like variable side wall angle (SWA), resist top loss (RTL), resist footing or undercut, etc., and none of this complexity can be captured in a 2D model. As the etch process that usually follows the litho step is expected to behave slightly differently in the presence of SWA or RTL, and can even lead to patterning failures depending on what the 3D resist profile actually looks like, there is a rapidly growing interest in what is now called R3D models for OPC, i.e., models that, at least to some extent, incorporate some information on how the printed resist pattern changes in

the z-direction. Other useful applications for R3D models would be SRAF printing (which sometimes takes place at the resist surface or bottom only) or other effects that preferably happen at the resist surface or the interface with the underlying substrate (such as footing or scumming).

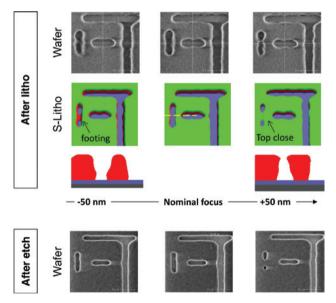

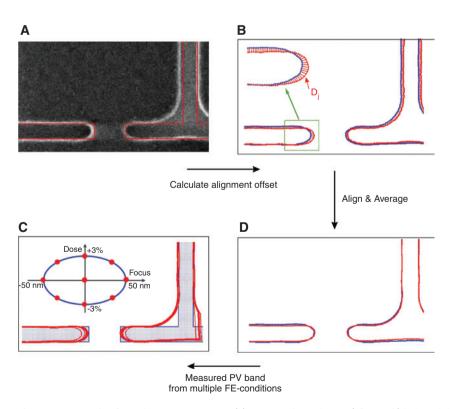

Rigorous lithography simulators like S-Litho and Prolith have always included this third dimension and, in fact, deliver a 3D resist profile. The example in Figure 5 illustrates this for the case of one if our N20 Metal1 patterns that we found to be weak after etch (i.e., having a limited process window), something which could be attributed to the resist profile being sloped at the position of the weak spot [26]. A similar literature example can be found in [27], where a rigorous simulator was also used as a 'forensic tool' to understand the cause of failures observed after etch. Although this use of rigorous simulators is quite valuable, one would like the OPC model to flag suspected resist profile-related hotspots before the mask is built, i.e., during the mask printability check that is done immediately after OPC ('computational verification', see Section 3.2). This, however, requires that the OPC model be extended into the third resist dimension, i.e., it requires R3D OPC models.

Extending the OPC models, themselves, to R3D has not been all that difficult. Indeed, the original R2D

**Figure 5:** Example of a potential R3D hotspot from our Tespa20 Metal1 test vehicle (i.e., trench printing), at nominal focus and at a +50 nm and -50 nm defocus [26]. The S-Litho-simulated resist profiles show a clear difference in resist profile for positive and negative defocus, in agreement with the observed after-litho top-down SEM images. After etch, these profile differences translate into a quite different result: at positive defocus, the short vertical trench disappears almost completely.

models – although confined to a single (x, y) plane at a certain vertical position  $z_0$  inside the resist – can be built at *any* value of  $z_0$ . Building multiple R2D models, each for a different  $z_0$  [28], was indeed the first step in the direction of R3D. (An example will also be shown in Figure 16). What is missing in this initial approach, however, is vertical diffusion, i.e., the fact that chemicals inside the resist are not confined to a single xy-plane (as R2D models implicitly assume) but also move in *z*, thereby effectively coupling the xy-planes together. Today, all major EDA companies have extended their models with some vertical-diffusion mechanism [29–31], and some initial validation of their models has been published, e.g., by comparing their predictions with the results of a rigorous simulator [29] or with printed wafer data [34].

If the mathematical framework for R3D models seems essentially ready or at least known, the real problem with R3D models is how to calibrate them, as this requires reliable wafer data on actual resist profiles, preferably for a reasonably large set of structures and preferably including different types of structures. That is not obvious.

One technique that has the potential of yielding resistprofile information and that has a short measurement time (which means that measuring a lot of structures is feasible), is scatterometry, also called optical CD (or OCD) metrology. Application of OCD for OPC purposes has, indeed, been tried for both 1D and 2D structures (see, e.g., [28, 32, 33]), and although some of the initial results were promising, it seems that the momentum to use OCD for resist-profile measurements has largely faded away. The number of variables that need to be included in the OCD models (that fit the measured spectra and convert them into resist profile information), simply seems too large to obtain reliable, absolute values for, e.g., SWA or RTL. This is even more so if the wafer stack used contains multiple layers beneath the resist or if 2D patterns need to be measured, in which case the number of geometrical parameters increases rapidly.

Cross section SEM (XSEM) or atomic force microscopy (AFM) has, of course, been often used to measure resist profiles. But both techniques are slow and not applicable to all the structures that are usually included in resistmodel calibrations for OPC, such as 2D structures (XSEM) or narrow isolated spaces (AFM). Nevertheless, an R3D model that was recently built from XSEM and AFM data [35] has shown some promise. Whether enough XSEM/ AFM data can be collected to build a model that can be applied to a wide variety of structures still remains to be demonstrated.

Another approach that has recently been taken [29, 34] is to use rigorous simulators to generate resist-profile

data for many structures and use that data as input for an R3D model calibration. Rigorous simulators do not require a large set of measured structures to build a model from, and once a calibrated resist model is available, it can be used to calculate resist profiles for as many structures one wants, both 1D and 2D. The Achilles' heel in this approach is, of course, the question how accurate these simulated profiles are. Also, this approach would, therefore, require further validation.

The conclusion of this section – at least today – seems to be that there is an increasing demand for R3D models, but that there is no proven nor accepted path to generate the calibration data it requires. We, therefore, expect continuing efforts in this field. An evolution that will relax, to some extent, the need for accurate R3D models or the variety of structures they should cover, is the trend toward simpler and more regular layouts (which we will discuss in Section 5).

### 2.1.4 Effect of a non-uniform wafer substrate: Wafer 3D

Wafer topography effects or Wafer 3D (W3D) effects are not an issue for most process layers: the top surface of the wafers is usually planarized, and the use of some antireflective strategy effectively 'hides' any buried topography below the surface. There is (or was), however, one exception, namely, the implantation steps that occur in the front-end processing. The use of a Barc adds to cost and also poses technical difficulties in these cases, which is why a Barc was traditionally not applied for implantation layers: the resist is spun directly on the post-Active or post-Poly wafer topography. This means that the implantation exposure is affected by reflections from the substrate (which are different on Si, oxide, and poly-silicon), as well as by the wafer topography of Active or the combined topography of Active and Poly. These implantation layers were long considered to be noncritical layers for lithography, such that W3D effects could be ignored or could be dealt with by using simple rule-based corrections, but with recent nodes, this has gradually been changing. W3D effects have become quite severe, and as correct implantation profiles are key to the device operation, an increased interest to include actual W3D modeling into the OPC flow can be seen in the literature since about 2009.

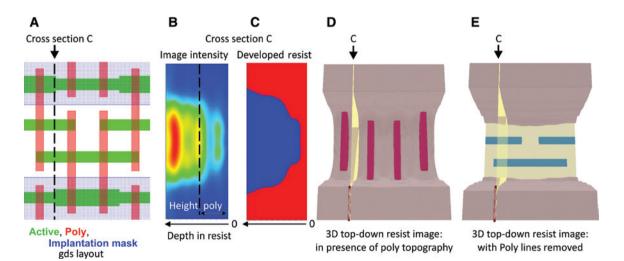

Rigorous simulation solutions to wafer topography effects have existed for quite some time (see, e.g., references [36–38], but these again use methods (e.g., finite element, FEM, or finite-difference time domain, FDTD) that are far too time consuming to be applied full chip.

So, over the last few years, a number of approaches have been developed each of which provide a way to incorporate W3D effects by adding extra terms to the intensity calculation, to take into account the reflected light from the various patterned areas on the wafers, as well as (at least in the most elaborate schemes) the interference between this reflected light and the incoming light.

The exact details of the different methods are not public, but they all start from traditional model(s), i.e., models assuming a flat, uniform substrate. The light intensity calculated with these models is then 'corrected' with additional terms, representing the nonuniform reflection and - sometimes - also interference terms. An initial approach to obtain these extra terms [39-42] was to define one or several 'virtual' or 'fictive' masks, derived from the Active (and Poly, in case of a post-Poly implantation) mask, from which these extra intensity terms were then calculated. One way to include interference terms between incoming and reflected light is to define a set of appropriate kernel functions for mixing the incoming and reflected waves that are defined such that the resulting model fits measured CD data from actual topographical wafers (see, e.g., reference [43]). Two other approaches that tried to tackle the problem in, perhaps, a more physical way can be found in reference [44], where a fast EMFsolving algorithm (called the 'generalized source method') is used, or in [45], where the wafer image is calculated with a method using a library of rigorous EM fields.

Most of these recent papers (and the references they contain) use actual wafer data to verify and demonstrate the concept they propose. Also, several EDA companies now have a W3D module in their OPC software packages. However, it also seems clear that the traditional approach to do the implantation litho steps without Barc or another planarizing approach is becoming untenable. With shrinking dimensions and increasing topography that comes with the introduction of Fins instead of STI (Active), it is increasingly difficult (to impossible) to keep avoiding the use of Barc or another planarization approach in the implantation steps. Reference [46] shows wafer data and rigorous simulations of combined Fin-Poly topography from a 10-nm node example, where the topography is such that it is not possible any more (at least at some positions) to get enough light intensity down to the bottom of the resist layer to clear the resist. Figure 6 shows a similar example for a planar technology SRAM case.

That is something OPC cannot correct but needs to be solved by a modification of the patterning process. For a while, the hope has been that wet-developable Barcs would solve this issue, but this idea seems to be abandoned today, which means that more traditional planarizing approaches have to be used. If this becomes the mainstream approach for the most advanced nodes, the need for an interest in W3D modeling is likely to fade away again.

**Figure 6:** Prolith simulations for a post-Poly implantation step on a planar SRAM case (28 nm node, i.e., Poly pitch of 110 nm), (A) Different mask layers in gds; (B) Prolith-predicted image intensity (cross section along plane C); (C) predicted resist profile (in the same cross section plane); (D) 3D top view of the predicted resist pattern in the entire simulated area. The Poly lines, themselves, emerge from the resist, but in between the poly lines, the resist is not cleared. (E) The same resist simulation in the absence of the Poly lines: then, the resist clears nicely (showing the active areas at the wafer surface), so it is really the Poly topography that 'prevents' the light from reaching the resist bottom. In case of a FinFet-type Active (instead of planar), this issue only becomes worse.

### 2.1.5 Laser bandwidth

Especially in 193-nm exposure systems, the projection lens has a non-zero longitudinal chromatic aberration, characterized by a quantity  $F_{\lambda} \equiv dF/d\lambda$ , which gives the shift of best focus with a laser wavelength change. The laser itself is non-monochromatic but has a finite bandwidth, and it has been shown that this induces CD changes for every structure (changes compared to the hypothetical monochromatic laser case) that can be approximated as [47]

$$\Delta \text{CD} \approx M_2 F_{\lambda}^2 Q_F \propto \text{E95}^2 F_{\lambda}^2 Q_F$$

(3)

where the second moment, M2, and E95 are metrics that characterize the laser bandwidth [47], and  $Q_F \equiv \frac{1}{2} d^2 CD/dF^2$  is the 'quadratic focus sensitivity' of the printed structure under consideration. So this equation tells that the finite laser bandwidth modifies the optical proximity, an effect that scales with  $Q_F$ . Most often, the OPC software assumes a monochromatic laser, which means that the  $\Delta CD$  effects of Eq. (3) will be absorbed into the resist model.

It is, however, possible to incorporate a laser bandwidth effect into the optical OPC models by calculating the intensity in the image plane as a superposition of contributions from separate laser wavelengths, each generating a best-focus plane at a slightly different position (consistent with the value of  $F_{\lambda}$ ). An example of such an approach can be found in reference [48].

### 2.1.6 Stray light (or flare)

Stray light, also called flare, occurs due to light scattering along the optical path between the mask and the wafer and results in a blurring of the optical image. This blur is usually described by a stray light or flare point spread function ( $PSF_{SL}$ ). It has been shown that flare adds an additional intensity at position r=(x, y) that can be approximated as [49]

$$\Delta I_{SL}(\mathbf{r}) \approx PSF_{SL}(\mathbf{r'} \cdot \mathbf{r}) \otimes I(\mathbf{r'})|_{\mathbf{r'} < \mathbb{R}} + PSF_{SL}(\mathbf{r'} \cdot \mathbf{r}) \otimes D(\mathbf{r'})|_{\mathbf{r'} > \mathbb{R}} + cst$$

(4)

The first term in this equation is a 'short-range' contribution that gives the scattered intensity at r from position r' not too far away from r: this contribution convolutes the no stray light intensity function I(r') with PSF<sub>SL</sub>. Scattering contributions from positions r' farther way from r (second term) are calculated with a similar expression, except that now, the convolution with the PSF can be done with a more coarsely calculated 'image', for which one can use some grayscale or mask density function, D, to speed up

the calculation. The transition distance R can be chosen somewhat arbitrarily. The  $PSF_{SL}$  function can often be described by a fractal or double fractal function [49–51]. From Eq. (4), it follows that the stray light-induced intensity change will be largest from the mask with a high transmission and negligible for very dark-field masks.

Stray light levels are usually small enough in modern optical lithography scanners (i.e., operating at 193 or 248 nm), such that OPC typically does not need to take it into account. The situation is different, however, in EUV lithography: the amount of light scattered from a surface with a given roughness is approximately inversely proportional with the square of the wavelength. Whereas in optical lithography, flare is often caused by contamination of certain optical surfaces, in EUV, the smoothness of the mirrors themselves, is the determining factor. Although flare levels of the latest generation EUV tools have gone down significantly compared to the earliest EUV tools, OPC for EUV will, in general, try to correct for it, especially in the case of masks with a high reflectivity or with high reflective areas. More detailed discussions of the role of flare in EUV lithography and on how it can be measured can be found in references [50, 51]. Today's OPC tools for EUV applications are well equipped to take flare into account during the calibration of OPC models as well as during the OPC mask-correction phase [52]. For a given mask and  $PSF_{SL}$ , they essentially pre-calculate  $\Delta I_{cr}(r)$  of Eq. (4) for the entire mask (this function is often called the 'flare map') and then add this intensity to the no-flare intensity expression of Eq. (1) during the OPC calculations.

### 2.1.7 EUV mask shadowing and other EUV-specific effects

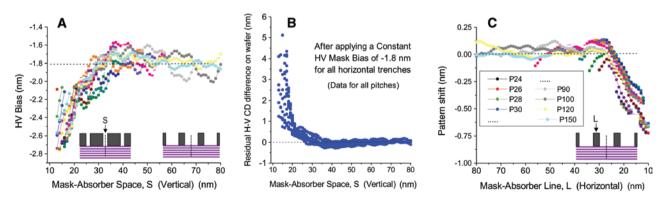

EUV lithography presents a few additional proximityrelated challenges that do not exist in optical lithography. The most important of these is the so-called shadowing effect [53–55]. EUV masks are reflective masks, which implies that the average angle of incidence of light from the illuminator cannot be at 90° to the mask surface but needs to be offset by a small angle  $\varepsilon$  (today  $\varepsilon$ =6°). This implies that mask structures with a different orientation will be illuminated differently, the result of which is that both the printed CD and the pattern placement will not be the same. Figure 6 illustrates the CD difference between horizontally (H) and vertically (V) oriented trench array structures. The CD and placement differences also change cross the slit. These effects need to be corrected for.

The initial approach to solving the H-V printed CD difference was to apply a constant H-V bias on the mask, i.e., shift the horizontally oriented absorber edges with a fixed amount with respect to their design target position. It was, indeed, found from rigorous calculations that the H-V bias needed to completely eliminate printed H-V CD difference was almost constant for 1D structures except at the smallest dimensions (mask space width below ~20 nm at 1×). Figure 7 illustrates this.

The constant H-V bias leaves, however, some residual CD differences and even breaks down for small 2D structures [55]. With the tight tolerances that need to be put on the dimensions for which EUVL can be expected to be used, a more accurate approach is desirable. Fortunately, efficient M3D solvers are now also available within the OPC packages for EUV [52, 56]: in principle, these should capture the variation of the shadowing effect for different structures and through the exposure slit and, hence, make the constant bias approximation unnecessary. Reference [56] demonstrates that the M3D model used produces results that are very close to those of a rigorous simulator.

The situation of the shadowing-induced pattern shifts is somewhat different. Although these pattern shifts are, in reality, several nm, the alignment of the mask before a wafer exposure will detect and correct the pattern shift of the alignment marks, before the exposure begins. This means that the OPC tool only needs to deal with structureand slit position-dependent placement error *differences*. Reference [56] shows that M3D models of today's OPC tools can also correct for these.

OPC for EUV has been demonstrated for a number of cases; see, for example, references [57] and [58]; the latter also includes a discussion of residual error mechanisms and, hence, where further improvements in the OPC modeling are required or desirable.

If EUV tools move into higher NA values, additional effects will grow in importance. One is the angle of incidence dependence of the multilayer reflectivity of the mask [59]. Also, this type of effect will then need to be addressed in the OPC modeling. EDA companies are currently incorporating this effect in their software.

### 2.2 Resist model

The approach to generate the resist model is fundamentally different from the approach to generate the optical model. Whereas the optical model is based on first principles, though with approximations made to meet the desired balance between rigor and speed, the resist model is essentially an empirical model that is fitted to measured wafer data. Even in rigorous lithography simulators, not all the processes that play a role in converting the 3D image intensity in the resist film into a developed, threedimensional resist pattern are completely understood, let alone correctly modeled in all their complexity, and yet, the resist part of the (rigorous) simulation takes a large fraction of the simulation time.

OPC modeling has, therefore, taken a different approach to the resist model: it applies some 'mathematical conversion' to the calculated intensity, I(x, y), that eventually predicts where the resist will be developed away and where it will stay. Every EDA company has its own specific approach. Common is that this 'conversion operator' contains enough degrees of freedom as well as a set of free parameters that can be fitted to a set of CD data that are measured from a printed wafer: the calibration data set. (Examples of such empirical model forms can be found, e.g., in [4, 60].) The challenge is then to construct

**Figure 7:** Shadowing simulation example: trench printing (NA=0.33, Annular 0.9/0.65, Image-in-Resist model). Simulation for pitches (P) ranging from 24 nm to 150 nm. (A) Simulated HV Bias for each individual structure. (B) Residual H-V wafer CD difference, if all horizontal structures on the mask are corrected with a fixed HV-Bias of -1.8 nm. (C) Pattern displacement of horizontal trenches (assuming that the pattern shift of very large structures has been automatically corrected for during the reticle alignment in the scanner).

this calibration data set in such a way that the resist model that is fitted from it is also capable of predicting the resistprinting behavior of structures that were *not* included in the calibration. The art of generating an accurate resist model, therefore, consists of

- defining an appropriate calibration-structure set,

- generating high-quality CD data for these structures,

- calibrating the resist model by fitting it to the calibration data,

- verifying that the model can, indeed, be reliably used to be applied to all the structures that can occur in the targeted application. This verification step makes use of a second set of wafer measurements, independent of the calibration set. The model quality is then assessed by its ability to predict the CDs of these verification structures.

The metrics that are being used to quantify the quality of either the calibration or the verification steps are, therefore, based on the difference between the measured and modeled CD of each individual structure j:

$$\Delta \text{CD}(j) \equiv \text{CD}_{\text{modeled}}(j) - \text{CD}_{\text{measured}}(j)$$

(5)

Although these individual model residuals are ideal for detailed analyses (looking for trends, for example), it is also convenient to reduce such a large number of values into more compact metrics. For example, specifying how many percent of a certain structure type (e.g., 1D, Line-Ends, ...) have a  $|\Delta CD(j)|$  below a certain target value,  $\Delta CD_{min}$ , a quantity that we call the 'In-Spec Percentage' (or ISP). Often used is also the RMS value over all the  $\Delta CD(j)$  values [4],

$$\operatorname{ErrRMS} = \sqrt{\Sigma_{j} \Delta C D_{j}^{2} / N}$$

(6)

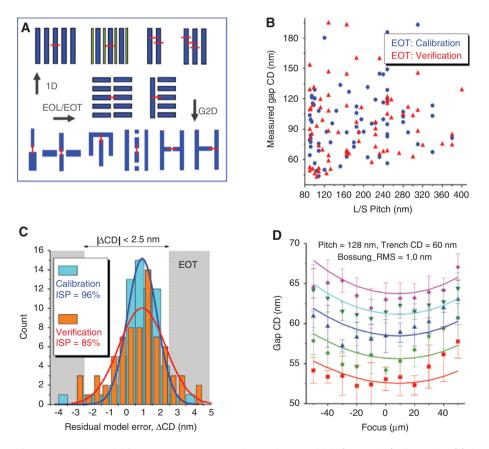

even though such a single-value metric can be deceptive: a low RMS value does not exclude that the model fails for a very small group of structures. Figure 8 shows an example

**Figure 8:** Resist model for OPC on our 20-nm node Metal1 test vehicle (NTD resist), illustrating (A) the type of calibration structures we used, (B) Pitch-gap combinations for the End-of-Trench (EOT) structures in the calibration and verification structure sets, (C)  $\Delta$ CD histogram and ISP (in-spec percentage) values of the EOT CDs of calibration/verification, (D) example of a measured EOT Bossung curve (part of the calibration structures) and its model prediction (line curves). Line-end control is very important for metal layers; hence, the emphasis on the line end OPC model performance in this example. The Bossung\_RMS value is calculated as in Eq. (6), but using only the  $\Delta$ CD<sub>j</sub>(F, E) values of this particular L/S structure j.

of some of the elements we just mentioned, for the case of our 20-nm node Metal1 OPC resist model.

In the following subsections, we will discuss each of the steps that should lead to a (hopefully) good resist model separately. Important to note, however, is that even when a model of the required accuracy is obtained, its validity is, in general, only guaranteed for the specific conditions (wafer stack, resist process, scanner settings, mask type) at which it was calibrated. If any of these conditions is changed, the model at least loses accuracy or becomes invalid altogether.

### 2.2.1 Selection of calibration structures

The key requirement for defining the calibration structure set is that they need to be 'representative' for the target application, which means that the model created with these calibration structures should be able to predict all the structures that can occur in the final design to which the model will be applied. Another way of formulating this, is saying that the calibration structures must be consistent with the design rules (DR) of the target application. At the same time, the size of the calibration structure set needs to be small enough to keep the time needed to measure all these structures within reasonable limits. It is because of these two competing requirements that people have been working on methodologies for efficient selection of calibration structures.

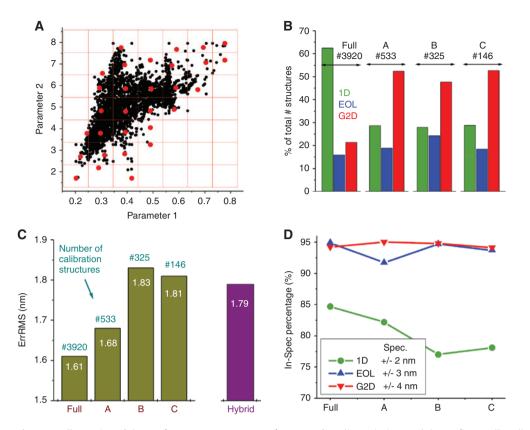

An initial approach, that has - with many variations become quite commonly used, uses the approach of sampling a structure parameter space (PS) of some kind. This method originated from Mentor Graphics' VT5 method [60] in which the printing of a given mask-polygon edge is related to a number of properties of the image intensity around that edge: Imin, Imax, Slope, and Curvature. This led to the idea [61–63] to represent potential calibration structures themselves, as points in a multidimensional image-parameter space (IPS, four dimensional, if the four parameters used are Imin, Imax, Slope, and Curvature. The concept can be extended to more or to other parameters). The assumption then is that structures that are close to each other in this IPS are 'similar' to each other, from which the idea follows to select structures for resist model calibration such that they cover the entire space, e.g., by sampling this space along some uniform grid (see Figure 9A). The IPS concept is not exclusively linked to the four 'original' VT5 parameters, nor to the use of a specific EDA tool. We have, for example, used S-Litho to calculate the parameters for a contact-hole EUV model, using a five-parameter space [57], selecting structures

from a few hundred thousand candidates. Figure 9 shows another example case from our own work (resist-line printing, with 193i), in which a selection of ~150 structures out of an original 4000 calibration structure set was found to deliver a model that was only slightly worse than the original 4000-structure model (i.e., the total RMS is only slightly higher, and the ISP values slightly lower: see Figure 9C and D).

Several further developments of these original concepts have been reported as well. Physical image parameters such as Imin, Imax, and Slope are clearly not independent parameters, so Singular Value Decomposition (SVD) techniques have been used [64, 65] to generate a new, orthogonal parameter set from the original (non-orthogonal) image parameters, thereby, further reducing the number of calibration structures needed. Extra parameters have been added to include through PW variations or sensitivity to mask errors, and sampling of the parameter space has been based on the identification of clusters of structures, rather than applying a uniform sampling [65]. One EDA company has developed a parameter space based on orthogonalized CD sensitivities [64]. Parameter space sampling methods appear very common now and have been successfully used by many.

It has, however, also been claimed that an approach based on image parameters only does not always lead to a representative structure set [66], and even though there can be other causes in the case of a failing model than just the content of the calibration set, it is true that the meaningfulness of any parameter-space approach depends on the relevance of the parameters chosen. There is, for example, no proof that the four original image parameters, or any alternative set, are the only parameters that matter in the conversion of an intensity distribution into a resist pattern. In that sense, it is the success of its use that justifies its applicability. Also the turn-around time for calibrating a model remains a concern. So improved structure sampling methods are still being tried; reference [67], for example, proposes a new mathematical formulation based on certain objective functions that can be specified according to the requirements of the process layer under consideration. This, the authors claim, leads to a further reduction of the amount of calibration structures needed.

If the trend toward more regular design styles is continued (see Section 5), it can, however, be expected that structure selection becomes easier again (at least for some layers) because of the much reduced variety of structure types in the target layouts. Let us elaborate on this for a moment. In Section 5, we will show that there is a trend to what is called unidirectional layouts for many layers, including the metal layers. If we now look at the OPC

**Figure 9:** Illustration of the IPS (Image-Parameter Space) concept for a line-printing model case (internally called 'OPC6': PTD, 193i, NA=1.2, min. pitch 100 nm). (A) The concept of IPS sampling, assuming – for simplicity of the drawing – a two-dimensional IPS space. The black points represent all candidate structures; the red points are the calibration structures selected by picking out one structure from each grid cell. (B) Four calibration sets were generated, starting from a very large set of 4000 structures and then using the IPS sampling technique to generate three smaller selections, labeled A to C. This plot shows the relative content of each of these structure sets. (C) ErrRMS using the full 4000 structure set as verification set for the models generated with the four calibration sets. Even the smallest structure sets offer a verification ErrRMS that is only ~10% larger than the one from the original model. (The Hybrid model is a model based on mixed use of CDs and SEM contours; see Section 2.2.3.) (D) In-Spec Percentage values obtained with the four models.

models of both Figures 8 and 9 and assume that bidirectional calibration structures are no longer needed (for modeling unidirectional layers), the size of the model-calibration data sets is reduced by more than 50%, which is quite considerable. The remaining structures would then still support a wide variety of structure sizes and pitches. Unidirectional layers, however, very often contain a limited set of pitches and sizes only, such that the amount of calibration structures then becomes very small indeed.

### 2.2.2 CD data quality

Even if one has succeeded in defining the perfect calibration data set, the resist model that is calibrated using it can only be 'as good as' the quality of the measured CD data. The necessity of good quality data is so obvious that this subject does not often get explicit attention in the literature. Especially with model calibration, experience teaches that even a few percent of 'bad data' can compromise the accuracy of the entire resist model. So we will use this paragraph to discuss some of the measures we have taken in our own work to avoid 'bad data'.

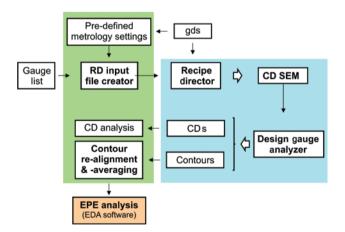

We find working with design-based metrology [68] indispensable. It allows fast and efficient generation of measurement recipes, especially if one builds some additional software on top of it (see also Section 4.1), in which the measurement position and settings are predefined for each structure type of interest. This ensures that no mix between different measurement conditions occurs, and complex measurement jobs of previously unmeasured structures can be created in minutes. Even more important is that it allows to inspect and (often) correct each individual measurement on an off-line station, after the SEM recipe has been executed (see illustration in Figure 10). Small mistakes of, e.g., the placement of the measurement boxes can be repaired, and even though this is tedious and time consuming, we find this well worth the

**Figure 10:** (A) Example of a misalignment between the measured SEM image and the design pattern (red lines), as a result of which the measurement boxes (white) and the edge detection are also off. (B) On the off-line Design Gauge Analyzer station, such errors can be (manually) repaired, thus, ensuring the quality of all CD data.

effort if something precious as the calibration of an OPC model is at stake. (We adore automation, but not every-thing can or should be automated).

Measurement statistics is the next concern [69]. Measurement of 2D structures (e.g., line ends) has a higher noise level and, therefore, requires a larger number of individual measurements to average. This requirement can be taken into account, to some extent, when designing the calibration structures on the test mask, by providing large-enough test structures such that multiple measurements can be made, one close to the other. This makes a separate pattern recognition and image refocus unnecessary for each individual measurement and, hence, makes doing more measurements less expensive without loss of accuracy.

Data filtering is equally important, but needs to be done with care. We typically use a histogram filter that verifies that the measured data constitute a single distribution and only delete data points that clearly do not fit into that distribution. When the distribution itself looks suspicious or when it is too wide (in comparison with similar structures), the entire structure is rejected from the calibration set.

We also check the exposure latitude for all structures: structures with an exposure latitude below a selected threshold are again rejected.

Finally, we visually inspect SEM images for all structures, to eliminate those that visibly do not print well, but have managed to survive all the automatic data filtering.

Apart from the random noise, systematic effects that affect the measured CDs are an increasing concern. The choice of the measurement algorithm is one; e-beaminduced resist shrinkage is another [70, 71]. Although it is possible to estimate the amount of shrinkage and, hence, correct the data for it (by measuring at multiple e-beam doses and extrapolating the data to dose zero), it is not clear to what extent this is being done in practice. To our knowledge, the impact of SEM shrinkage on OPC model accuracy has not been discussed in the literature. A thorough discussion of the subject of SEM-induced resist shrink is beyond the scope of this paper; for a recent discussion, see [72] and the references within. It may become necessary at some point to develop SEM-induced resist shrinkage models for OPC-modeling purposes.

### 2.2.3 CD vs. contour metrology

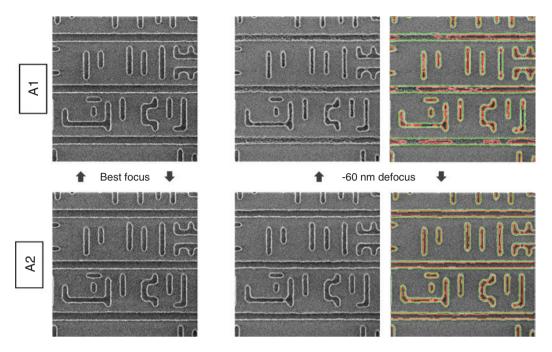

A CD-SEM image (especially of 2D structures) would appear to have a so much richer content than the few CD measurements that one usually extracts from it. This explains the attractiveness to use SEM image contours, representing the complete shape of (part of) the image for OPC modeling purposes, as an alternative to the traditional CD-based model calibration approach [73]. Expected benefits could be that less SEM time is needed, and/or more accurate models might be obtained. Between this simple concept and its realization, there is, however, an impressive series of hurdles that must somehow be dealt with. Among these are potential SEM image distortion, orientation-dependent edge quality differences, resist shrinkage, alignment of measured contours, statistics (i.e., contour 'averaging') and elimination of 'lowquality' data (fliers), selecting representative structures (again) while avoiding redundancy in the image content, matching of contour data with CD data, etc. For a more detailed discussion of some of these challenges, see, e.g., references [74, 75]. Progress is being made, however, and

judging from recent literature (e.g., references [75, 76]) the use of contours for OPC modeling purposes is gradually gaining interest and acceptance, even though it has not (yet?) become mainstream.

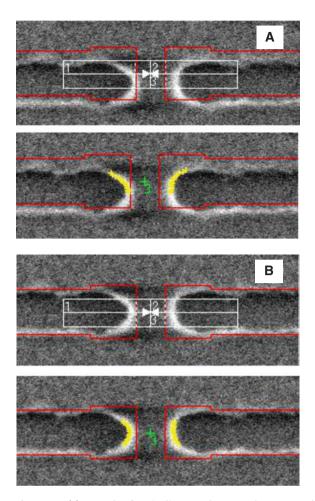

We will illustrate this by examples from our own experience in this field (also in Sections 3 and 4). Calibrating a model using contours relies on the measured Edge-Placement Errors (EPE) between the measured contours and the design target (or an ideal contour). This implies that the absolute position of the measured contour must be precisely known: any placement error goes immediately into the EPEs and compromises a good model quality. We have shown before that the contours delivered by the SEM vendor occasionally have a residual placement error [77]. Today, using more modern SEM tools, the situation has improved, but we still occasionally find residual alignment errors >1 nm (rising up to a few nm in more rare cases; Figure 11 shows a case where a relatively large alignment correction was needed), which is why we are still using our in-house software to re-align each measured contour, and - as a next step in the flow - calculate an averaged contour from a statistical set of contours, obtained from identical structures.

For each individual contour as well as for the averaged contour, one can quantify the deviation from the predicted contour using what we call the Contour\_RMS [77]:

$$Contour_RMS = (\Sigma_i D_i^2 / N)^{1/2}$$

(7)

$D_j$  are the point-to-point distances between the measured and the predicted contours, measured along the entire contour or along a selected clip.

Figure 11 also illustrates contour averaging and shows how a measured PV band can then be generated from averaged contours at multiple FE conditions (see Figure 11B).

Reference [75] describes an (also) in-house tool for analyzing (and, hence, selecting) potential calibration structures form an image-space parameter perspective. Reference [76] shows cases where the use of contours leads to increased model accuracy. It also applies recent technology [70, 71] for correcting measured contours for SEM shrinkage.

As improvements and experience builds up, it can be expected that SEM contours will increasingly find their way into the model calibration field, as they already do when it comes to model verification [78–80], as we shall see in Section 3.

**Figure 11:** Example of SEM image contour use. (A) Measured SEM image (after etch) in its original alignment to the mask gds; (B) extracted SEM contour (red) together with a predicted contour (blue) that is used for re-aligning the measured contour. (C) Result of the averaging of 15 re-aligned contours (red) overlayed with the predicted contour (blue); (D) measured PV band, obtained from averaged contours at multiple FE conditions (ellipse 'touching' ±50 nm defocus ±3% dose offset).

### 2.3 Additional models

Apart from the optical and resist models described in the previous section, the OPC engine can/must be fed with additional input. An important one is the specification on how to create Sub-Resolution Assist Features (SRAFs or simply Assists). These structures are put on the mask and should not print themselves but, when properly placed and sized, should make printing structures ('main features') more robust against process variations. In this era of limited DOF, SRAFs are now used, in particular, to increase DOF. The user will need to decide how these SRAFs should be placed and needs to take measures against assist printing. These are the issues of Assist placement and printing.

We already mentioned the possibility of also specifying a model that describes mask imperfections, the mask processing correction model (MPC). This model is optional: if no MPC is specified, the OPC engine will assume that the mask is perfect. Mask errors will then be 'absorbed' into the resist model, which does, in principle, compromise the predictive power of the OPC model. Nevertheless, MPC models does not seem to be commonly used.

Patterning does not end after litho: usually an etch step follows, and during this etch step, the patterned dimensions change again. So the OPC software should also include an 'etch model', i.e., a model describing how the pattern in resist (after litho) will be transformed into a pattern after etch, such that it is this final, after-etch pattern that is close to the design-target pattern.

Already in Figure 2, we showed an overview of the models that are being used (or can be used: not all are mandatory) in the OPC process. We will now discuss the assist- and etch-related models. At the end of the section, we will also add a note about stochastic effects.

### 2.3.1 Assist placement: model or rule

A first approach to assist placement is to use a 'rulebased' placement approach. Such a rule specifies how many assists, of which size and at which positions have to be inserted in-between two main features in the target design, depending on the space between these main target design features. For line- or trench-like patterning layers, such a rule is not very difficult to make and is usually based on the observed printability of a large number of test structures. We have made such rules in the following way, targeting at i) an optimized DOF for all structures, and ii) guaranteed assist nonprinting.

- Print a test mask that contains a large number of 1D structures (lines or spaces at a variety of pitches and with varying mask-line- or mask-trench widths) on which a (large) number of trial assist rules have been placed. Mark all the cases for which the assists are not printing, while the main feature prints approximately at the intended target CD. Do this inspection at nominal focus, as well as at under- or overexposed dose condition (for a bright-field mask/NTD combination or a dark-field mask/PTD combination, respectively). Cases with printing assists are eliminated from the list. The fact that assist nonprinting is ensured from printed wafers and not from some model is an important advantage of this procedure.

- Run the remaining assist-rule cases through a rigorous simulator (preferably with a calibrated resist model) and determine for every pitch which assist rule provides the largest DOF.

- Measure the best performing rule cases from the previous step on wafer, this time through focus, to make sure the intended DOF is reached. (If not, try more rules.)

The assist-placement rules generated in this way can be very successful in many cases. The requirement that assists should not print, can usually be met, as it is built into the rule-generation procedure and is obtained from printed wafers. Also, the assist placement is usually very good for patterns with regularly shaped spaces (between main features), but when the space is nonregular, the rule may not lead to a unique solution, but allows different implementations. The assist placement solution that is adopted may not be the real optimum, which can result in weak through-focus performance. Also, generating rules in this way is time consuming.

This is why people have tried to devise *models* for assist placement, the goal of which is to ascertain that also for complex main feature configurations, an adequate assist coverage is obtained. Many approaches have been tried, and the literature on this topic is quite extensive. Confining this discussion to the more recent history, the following approaches can be mentioned.

Generation of some pixel map that suggests assist locations. This concept first defines an objective function (defined on all xy positions where no main feature exists) that assigns a value to the usefulness of placing an assist at position xy with respect to the printability of the main features in its neighborhood. What this objective function looks like and which main feature printability metric is to be optimized does not need to be the same for all who have used this type of approach (and is often not publicly available). But this map is then used to insert assists at the most promising positions, after which a step to simplify the shape of the resulting assists is inserted, as well as a check that the assists will not print. Examples of such an approach can be found in references [81–83], where this pixel map is called the 'SRAF Guidance Map', the 'Cost Covariance Field' and the 'Gradient Map', respectively. Each of these approaches has demonstrated some level of success, and is relatively fast. Whether they succeed in making most or all target structures sufficiently robust, depends, of course, also on the soundness of the objective function they assume and the reliability with which they can estimate assist printability.

- 2) A different type of approach is called Inverse Lithography Technology (ILT). Originally, the ILT concept aimed at inverting Eq. (1), i.e., instead of calculating the image from a given mask function, it tries to calculate the mask function that leads to the required (or 'ideal') image [84, 85]. Note that this ILT approach does not only generate assist, but also the ideal shape of the main features, so it performs the assist placement and OPC step simultaneously. The difficulty, however, is that the ideal mask solution that results from such an inverted calculation usually has a continuously varying transmission and phase and would, hence, not be manufacturable. This means that this ILT-generated mask at least needs to be simplified to be consistent with the mask manufacturability requirements. This simplification can then be expected to lead to some loss in performance.

- 3) A more practical approach to the ILT concept is the pixel-inversion approach: for pixels outside the main features, the effect of inverting the mask from the design target transmission to the opposite (i.e., assist) transmission is evaluated, from which a decision to

convert this pixel to the assist tonality or not is taken. Also this technique leads to complex-shaped assists, such that again, a shape simplification step needs to be added, as well as an assist-printability check. It is this version of ILT that is being used today.

ILT-type approaches are expensive from a calculation time as well as a mask-making point of view. Instead of applying them to the entire mask, they are typically used in a more 'focused' way, e.g., for generating better assist-placement rules, or as local fixes of hotspots on layouts that were OPCed with more traditional approaches (see, e.g., [86]).

Each of the assist-generating methods that are being used today has reported successes, but each is also based on some assumptions, either in the underlying concepts (e.g., cost functions) or in their technical implementation. So probably, none of them can guarantee success in all cases, and further progress in this field can be expected.

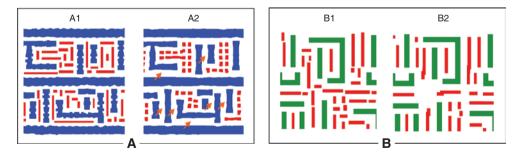

We conclude this section with two illustrations of the complexity of assist placement. Figure 12 shows two 20-nm node Metal1 patterns, one in which the rule-based approach was found to be better than the model-based approaches we tried, and one where a model-based approach is desirable. For contact or dot layers, the problem of assist placement is even more complex.

### 2.3.2 Assist printability model

Any model-based assist placement engine must also try to make sure that the assists will not print. Resist models calibrated from main features, as discussed in Section 2.2, are generally not reliable in making predictions about assist printing: predicting the behavior of assists would be a significant extrapolation from the structures that were used to calibrate the model. Also, using a simple threshold

**Figure 12:** Examples of different assist-placement scenarios. (A) Rule-based and model-based assist placement example, on the same M1A clip. In this particular example, the model-based case leaves some of the narrow spaces without assist (spaces indicated with arrow). As we have showed elsewhere [93], this limits the DOF in those areas; see also Figure 16. (B) Two implementations of the same basic rule for assist placement on the same clip of M1B (before OPC of the main features). Because the spaces between the target features are less regularly spaced, the actual assist arrangement can be quite different according to the details of the assist-placement setup.

model on the intensity at the assist positions is too simple an approach to be reliable enough. This means that a dedicated assist-printing model would have to be calibrated on measured wafer data from printing and nonprinting assists.

One difficulty with calibrating such a model is that the input data cannot be CD data: the most important condition that requires good prediction is the onset of assist printability. In that case, one cannot assign any reliable CD value to the assist. That is why the input data of such a model is often defined in a binary way, e.g., assigning a value 0 to nonprinting cases and 1 to printing cases (even though assigning a continuously varying printability value is possible as well, and should leads to easier modeling). Also, the onset of assist printing starts happening either at the bottom or at the top of the resist film (in clear-field or dark-field imaging, respectively). That is why it makes most sense to base assist-printability predictions on image intensities in a plane either close to the bottom or close to the top of the resist, i.e., in a different plane as the one used for the main feature model. This is the approach that was taken in references [87, 88]. The authors report an improved, though not yet perfect, assist printability with this type of approach.

A maybe better approach could come from R3D type models (see Section 2.1.3): in reference [30], a good reproduction of assist printing was obtained for the cases shown with an R3D compact model that was calibrated from rigorously simulated resist profiles. The real challenge of R3D models is – as we discussed above – how to calibrate them from wafer data.

### 2.3.3 Etch model

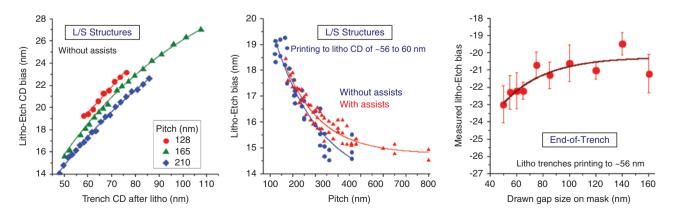

Patterning does not end after litho, it is usually followed by an etch step. Etch usually transforms the shape of the printed patterns in a way that is slightly different for each pattern, i.e., it contributes to the final proximity effect. Figure 13 illustrates this point for the case of our 20-nm node Metal1 etch process. The etch process was intended to shrink the litho dimensions – in this case, with 15 nm – an approach that is often taken to achieve small afteretch dimensions while keeping the litho process windows high. Figure 13 shows that the actual difference between the after-litho and after-etch CDs, which we call the 'etch bias', is actually structure dependent. Formulated in terms of pattern edge placement: not all edges shift with the same amount during the etch process.

For accurate final pattern control, this effect of etch needs to be included in the correction process. This is done in the way that was already shown in Figure 1: once the dependencies as in Figure 13 are known, the design target is converted into a litho target, displacing each edge (fragment) according to the effects that etch is expected to have on this edge. After that, the combined optical-resist model further converts this litho target into the actual OPCed mask.

The effect of etch can be described by a rule table or by a model. Although model forms to describe etch effects have been known for a long time (see, e.g., references [89, 90], until recently, there seems to have been a preference in the industry for a rule-based etch correction (for a discussion on this point, see reference [91]). One of the reasons for that was that etch effects have a longer range than optical and resist effects, which puts additional burden on the calculation time. But today, these computational issues can be efficiently dealt with, and with the ever increasing need for more accurate pattern control, a model-based approach is increasingly required. References [92, 93] show examples, where a model has been built on an etch-bias data set of which Figure 13 shows a

Figure 13: Examples of measured etch-bias dependencies for the case on an NTD resist on a SOC/SOG stack (case of our Metal1 LELE process). CD shrink during etch targeted at 15 nm (at ~isolated structures). The lines in the plots are exponential-fit curves through the data.

selection and afterward applied to 2D structures. We have used this type of modeling in the staged approach that is shown in Figure 1A for a successful combination of lithoetch proximity correction. So it seems that today's etchmodeling infrastructure is well capable of doing the job it was designed for.

### 2.3.4 Stochastic effects

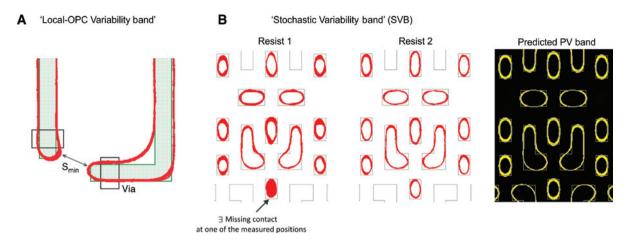

Also stochastic effects have an impact on the shape and especially the variability of printed patterns. Traditional lithographic modeling has always implicitly assumed that the resist is a continuum, but matter, as well as light, consist of particles, and at the dimensions, we are working today, this starts showing. LWR/LER are wellknown manifestations of this, but close to the printability limit, stochastic effects can lead to random printing failures ('stochastic failures'). Randomly missing contacts are just one example of this.