95% of researchers rate our articles as excellent or good

Learn more about the work of our research integrity team to safeguard the quality of each article we publish.

Find out more

ORIGINAL RESEARCH article

Front. Neurosci. , 24 March 2021

Sec. Neuromorphic Engineering

Volume 15 - 2021 | https://doi.org/10.3389/fnins.2021.644604

This article is part of the Research Topic Neuronal Diversity and Modular Functional Specialization: Understanding and Modeling from the Perspective of Spiking Neural Networks View all 8 articles

In this study, we propose an integrate-and-fire (I&F) neuron circuit using a p-n-p-n diode that utilizes a latch-up phenomenon and investigate the I&F operation without external bias voltages using mixed-mode technology computer-aided design (TCAD) simulations. The neuron circuit composed of one p-n-p-n diode, three MOSFETs, and a capacitor operates with no external bias lines, and its I&F operation has an energy consumption of 0.59 fJ with an energy efficiency of 96.3% per spike. The presented neuron circuit is superior in terms of structural simplicity, number of external bias lines, and energy efficiency in comparison with that constructed with only MOSFETs. Moreover, the neuron circuit exhibits the features of controlling the firing frequency through the amplitude and time width of the synaptic pulse despite of the reduced number of the components and no external bias lines.

Neuromorphic computing architectures mimicking the human brain have been used to perform pattern recognition, classification, and perception to overcome the crucial issue of power consumption faced by Von-Neumann computing architectures while processing complex data and information (Chu et al., 2014; Merolla et al., 2014; Srinivasan et al., 2017). Despite their advantages over Von-Neumann computing architectures in terms of energy efficiency, neuron circuits, driven by spiking neural networks (SNNs), still need more power for their integrate-and-fire (I&F) operations than biological neurons (Choi et al., 2018). For most neuron circuits, particularly those using complementary metal-oxide semiconductor (CMOS), feedback field-effect-transistor (FBFET), and floating gate FET (FGFET) (Indiveri et al., 2006; Kornijcuk et al., 2016; Choi et al., 2018; Kwon et al., 2018; Kim et al., 2019; Wang and Khan, 2019; Zhang and Wijekoon, 2019; Chavan et al., 2020; Woo et al., 2020), the presence of numerous transistors and external bias lines result in relatively high power consumption for the I&F operations. Thus, for energy-efficient neuron circuits, suppression in numbers of transistors, absence of external bias lines, and use of steep switching devices with extremely low subthreshold swings (SSs) are needed (Abbott, 1999; Izhikevich, 2003; Cheung, 2010); the steep switching devices are crucially necessary for a substantial reduction in power consumption of neuron circuits.

In this paper, we propose a neuron circuit without external bias lines and verify its I&F operation. The essential component of the circuit is a p-n-p-n diode that acts as a steep switching device with an extremely low SS for the I&F operation (Moll et al., 1956; Xiaodong et al., 2014). The presence of two terminals in the diode eliminates the need for external bias voltages for the I&F operation, and the low subthreshold current of the diode reduces the power consumption of the neuron circuit. Furthermore, the neuron circuit exhibits temporal integration, triggering threshold, depolarization, repolarization, and refractory period similar to the essential functions of a biological neuron (Bear et al., 2007). In this work, the I&F operation is investigated through the mixed-mode technology computer-aided design (TCAD) simulation (Silvaco, 2016). The firing frequency performance is evaluated by modulating the amplitude and time width of synaptic current pulses flowing into the neuron circuit. The energy consumption, power consumption and energy efficiency are examined and compared with those of a CMOS-based neuron circuit using a digital signal controller.

The dimensional parameters of a diode consisting of a p+-n+-p+-n+ silicon nanowire (SiNW) are a p+-doped (P1) region of 100 nm, an n+-doped (N1) region of 50 nm, a p+-doped (P2) region of 50 nm, an n+-doped (N2) region of 100 nm, and a channel thickness of 10 nm (see the inset of Figure 1). The doping concentration are 1 × 1020 cm–3 for the P1 region, 5 × 1018 cm–3 for the N1 region, 5 × 1019 cm–3 for the P2 region, and 1 × 1020 cm–3 for the N2 region. For the n-channel MOSFETs with n+-p–-n+ SiNWs utilized in the neuron circuit without external gate and drain bias, the dimensional parameters are a channel length of 50 nm, an Si channel thickness (TSi) of 10 nm, and a gate oxide thickness (TOX) of 2 nm. Doping concentrations of the n+-doped source, p–-doped channel, and n+-doped drain regions are 1 × 1020, 1 × 1017, and 1 × 1020 cm–3, respectively.

Figure 1 shows current-voltage characteristics of the p-n-p-n diode in a DC sweep of anode voltage. The p-n-p-n diode remains in the off state before the anode voltage (Vanode) is applied. As Vanode increases from 0.0 to 2.3 V, electrons in the n+-doped region (N2) and holes in the p+-doped region (P1) move toward the junction between the p+-doped region of P2 and the n+-doped region of N1. Subsequently, reverse bias is formed at the junction, which induces impact ionization with a strong electric field. When the reverse bias exceeds the breakdown voltage of the p-n-p-n diode, the diode becomes avalanche breakdown (Holonyak, 2001). The p-n-p-n diode has the latch-up properties with a steep subthreshold slope (SS) of 0.02 mV/dec and a high on/off current ratio of 109. These characteristics help the neuron circuit to generate the narrow spiking width, thereby providing the low power consumption, high energy efficiency and high firing frequency. In comparison, MOSFETs have a limit of the 60 mV/dec SS at 300 K, which is a major obstacle to reduce the operating voltage and power consumption due to the flowing subthreshold current (Lim et al., 2017). Consequently, a neuron circuit using only MOSFETs has the wide spiking width due to the subthreshold current.

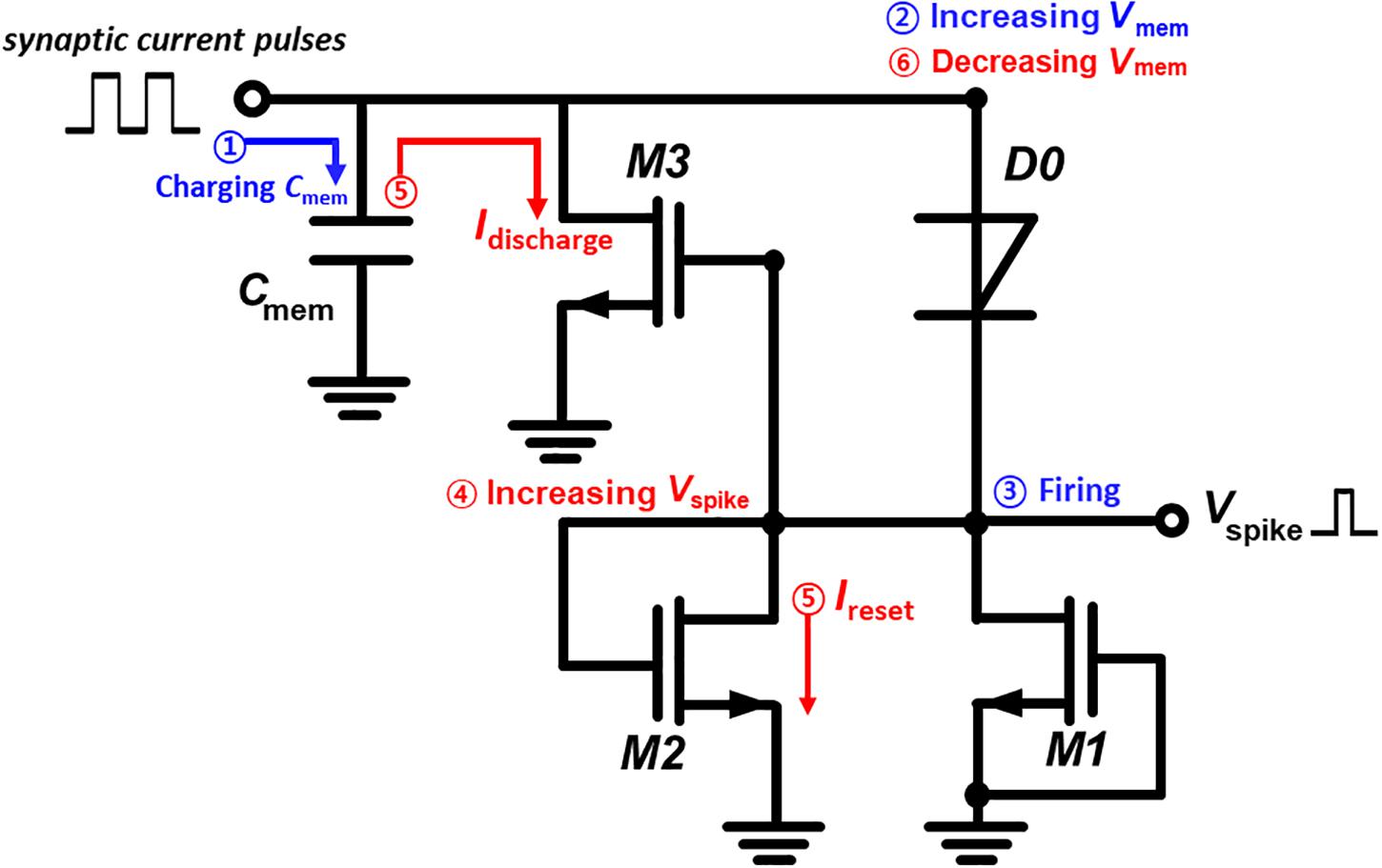

Figure 2 illustrates the construction and operation mechanism of the proposed I&F neuron circuit. The neuron circuit is constructed with one p-n-p-n diode (D0), three MOSFETs (M1, M2, and M3), and one membrane capacitor (Cmem). Regarding the roles of the components of the I&F neuron circuit, Cmem contributes to the increase in the membrane voltage (Vmem); D0 generates spike voltages (VSpike); M1 acts as a resistor and the resistance contributes to the determination of the VSpike value; and M2 and M3 are responsible for resetting the spiking and membrane voltages, respectively. For the operation of the I&F neuron circuit, M1 is in the cut-off mode because of the grounded gate, and M2 is in the saturation mode because of the connection of the gate to the drain; note that the threshold voltages of M1 and M2 are about 0.6 V. Both the resistances of M1 in the cut-off mode and M2 in the saturation mode determine the VSpike value by voltage dividing with the diode. Also, the M1, which has constant resistance from the cut-off mode, contributes to restrain unwanted charge-feedthrough caused by capacitive coupling between the M3 channel and its gate (for more details, see Supplementary Material). Most importantly, the presented neuron circuit operation requires no external bias lines.

Figure 2. Description and operation mechanism of the presented I&F neuron circuit without external bias lines.

The I&F operation of the presented neuron circuit begins with the flow of synaptic current (ISynaptic) pulses from pre-synaptic devices into the neuron circuit. Charges carried by the ISynaptic pulses are integrated into Cmem with a capacitance of 30 pF. The temporal integration of charges increases Vmem which is the anode voltage of D0. VSpike is abruptly generated when Vmem reaches a triggering threshold voltage of 2.26 V for the latch-up of the anode current of the diode. The VSpike value is determined by the voltage division of the diode and M1. The generation of VSpike supplies the gate voltages to M2 and M3 and opens the channels of these transistors. The discharge current flows from Cmem to the ground through the M3 channel, and this flow rapidly decreases Vmem. Simultaneously, the reset current Ireset flows from the cathode of D0 to the ground through the M2 channel. Eventually, the opening of the M2 and M3 channels resets the anode and cathode voltages to zero, and accordingly VSpike becomes zero. Thus, the latch-up of D0 and the subsequent opening of the M2 and M3 channels cause the presented neuron circuit to fire VSpike pulses toward post-synaptic devices.

Membrane current is the anode current flowing in the channel of D0 in the neuron circuit. The membrane current varies with Vmem (the anode voltage) as charges are integrated into Cmem and discharged from Cmem. The membrane current is plotted in Figure 3 as a function of Vmem. The plot demonstrates that the operation of the presented neuron circuit mimics the temporal integration, triggering threshold, depolarization, repolarization, and refractory period of a biological neuron. The membrane current does not flow during the temporal integration of charges in Cmem. When the temporal integration induces a triggering threshold voltage of 2.26 V, the membrane current increases abruptly to 130.9 μA. This abrupt increase in the membrane current in the neuron circuit corresponds to the depolarization of electrical action potential in a biological neuron. The discharging of Cmem after depolarization leads to a rapid and subsequently gradual decrease in the membrane current, which corresponds to the repolarization of electrical action potential in a biological neuron. As the membrane current becomes negligible, the presented neuron circuit remains in the refractory period.

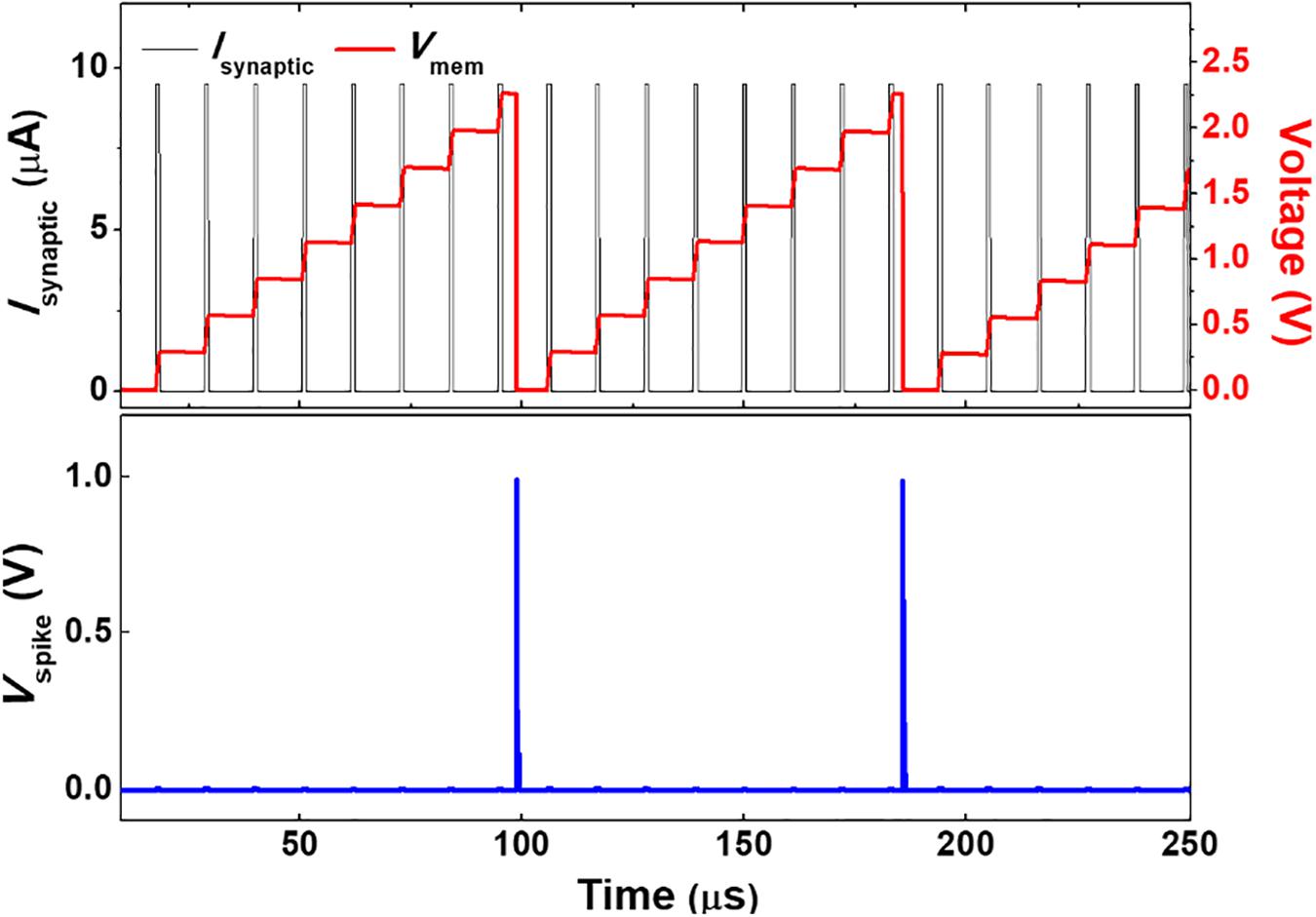

The synaptic current pulses, membrane voltage, and spike voltage pulses in the I&F operation of the presented neuron circuit are plotted in Figure 4 as a function of time. As the ISynaptic pulses with a time width of 0.8 μs and a period of 10 μs are transmitted to the neuron circuit, charges are integrated in Cmem, thereby increasing Vmem. Each ISynaptic pulse of 9.5 μA increases Vmem by 0.28 V during the temporal integration. When Vmem reaches the triggering threshold voltage of 2.26 V after the arrival of eight ISynaptic pulses into Cmem, VSpike is generated rapidly from 0.0 to 0.98 V during the depolarization. During the subsequent repolarization, both Vmem and VSpike return to the initial voltage of 0.0 V. Over a single period of the depolarization and repolarization, the presented neuron circuit fires a VSpike pulse with an amplitude of 0.98 V. For these ISynaptic pulses, the VSpike pulse is repeatedly fired at a frequency of 11.5 kHz.

Figure 4. Synaptic current pulses, membrane voltage, and spike voltage pulses of the presented neuron circuit as a function of time.

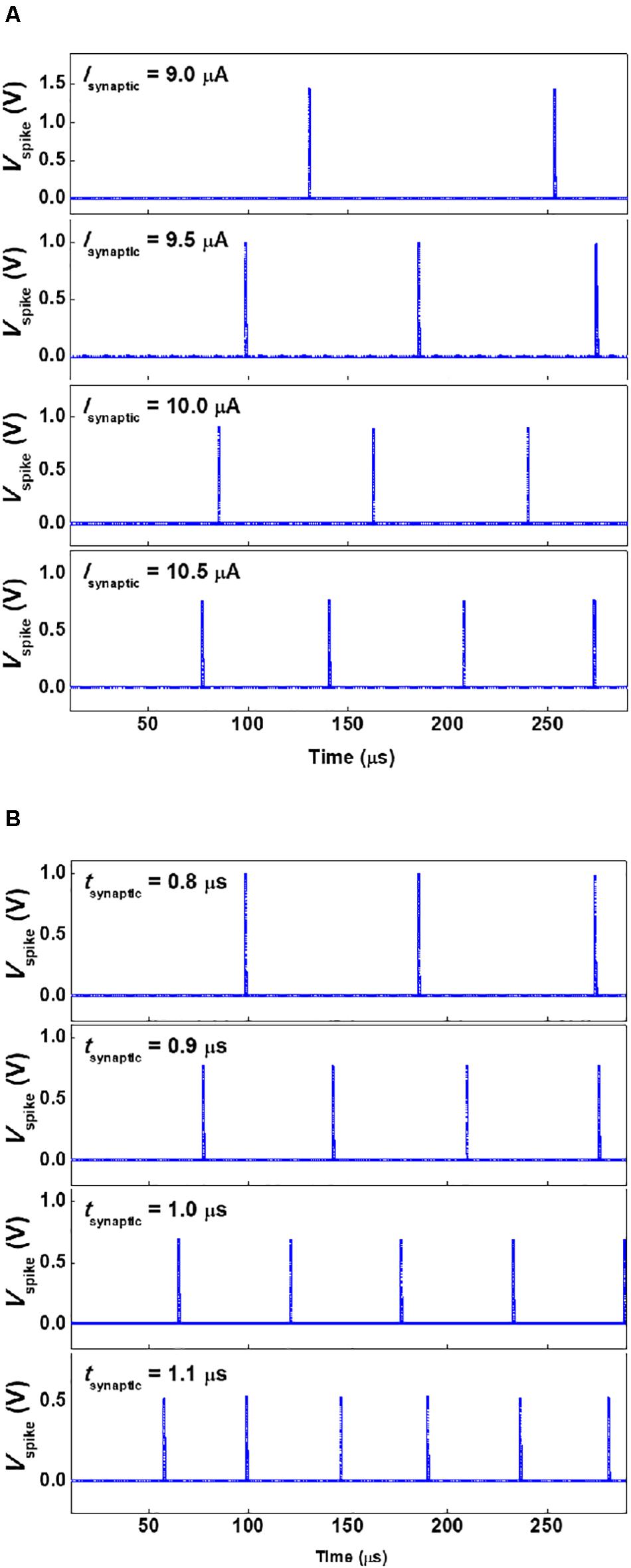

The firing frequency of the presented neuron circuit depends on the amplitude and time width of the ISynaptic pulses. This dependency of the firing frequency is depicted in Figures 5, 6. The larger amplitude or the wider time width of the ISynaptic pulses decreases the time for Vmem to reach the triggering threshold voltage. This causes the neuron circuit to fire the VSpike pulses at higher frequencies. The firing frequency increases from 8.1 to 15.6 kHz as the amplitude of the ISynaptic pulses with a time width of 0.8 μs and a period of 10 μs increases from 9.0 to 10.5 μA by an increment of 0.5 μA. Moreover, the firing frequency shifts from 11.5 to 24.0 kHz as the time width (tSynaptic) of the ISynaptic pulses with an amplitude of 9.5 μA and a period of 10 μs increases from 0.8 to 1.1 μs by an increment of 0.1 μs. The adjustment of the amplitude and time width of the ISynaptic pulses control the firing frequency (for more details, see Supplementary Material).

Figure 5. Firing frequency as a function of time for the (A) ISynaptic amplitudes (with a time width (tSynaptic) of 0.8 μs and a period of 10 μs) from 9.0 to 10.5 μA by an increment of 0.5 μA, and (B) ISynaptic time widths (with an amplitude of 9.5 μA and a period of 10 μs) from 0.8 to 1.1 μs by an increment of 0.1 μs.

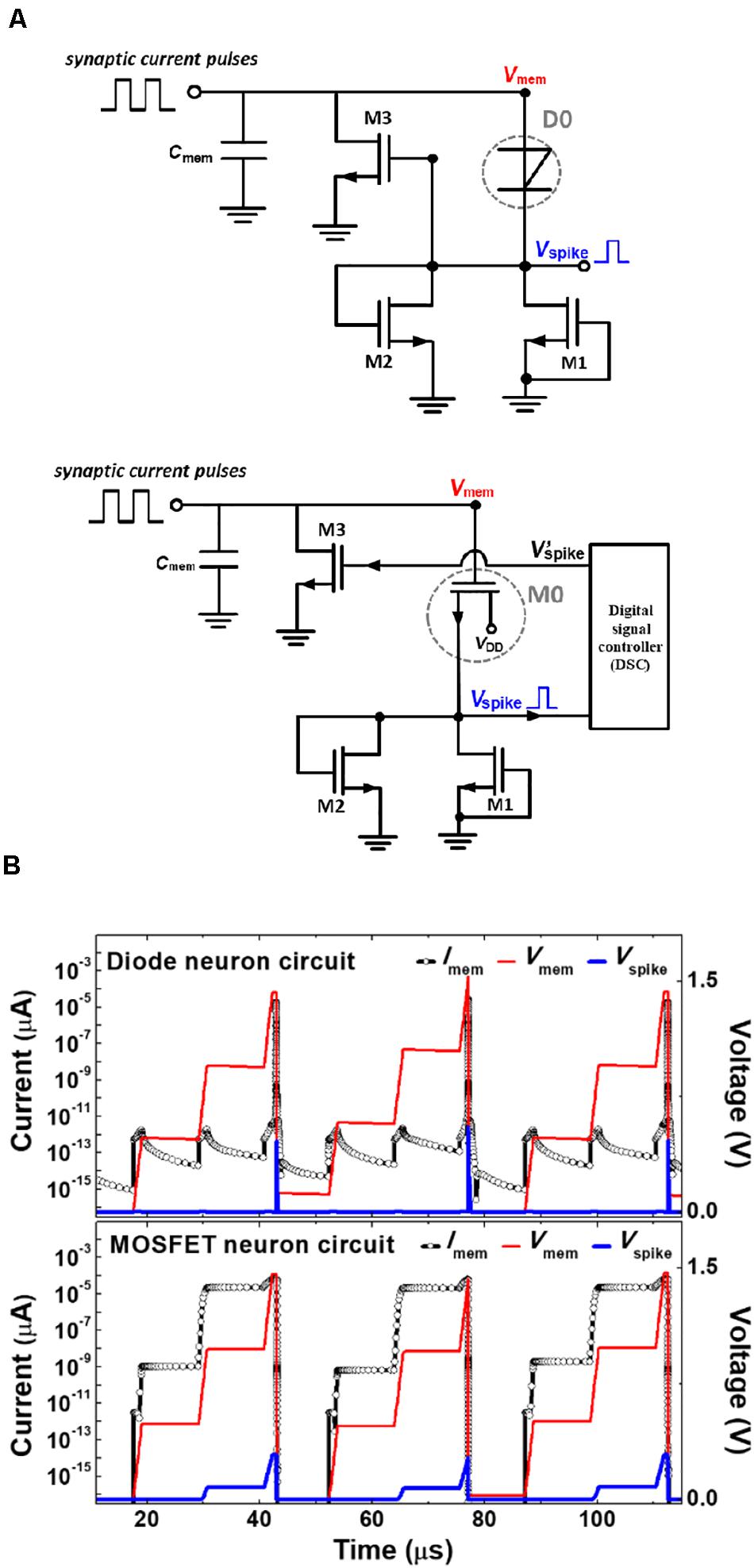

The p-n-p-n diode (D0) utilized in the presented neuron circuit is replaced by a MOSFET (called M0) for the construction of a MOSFET neuron circuit to emphasize the advantages of the use of a p-n-p-n diode in the presented neuron circuit over the MOSFET neuron circuit, regarding the energy consumption, power consumption and energy efficiency. The structure and function of the MOSFET neuron circuit are compared with those of the diode neuron circuit in Figure 7. The MOSFET neuron circuit needs a digital signal controller for the I&F operation; the digital signal controller supplies driving pulses to reset the MOSFET neuron circuit when the membrane voltage reaches a threshold voltage of M0. In the MOSFET neuron circuit, Vmem provides a gate voltage of M0, and the triggering threshold voltage for the opening of the M0 channel is 1.44 V. However, for Vmem below 1.44 V, VSpike is already generated because the SS is higher than 60 mV/dec, which forms a greater VSpike time width than when the diode is used; this causes the circuit to consume energy more inefficiently while VSpike is generated.

Figure 7. (A) Schematic diagrams of the diode neuron circuit and the MOSFET neuron circuit with a digital signal controller, and (B) synaptic current pulses, membrane voltage, and spike voltage pulses as a function of time for the diode neuron circuit and the MOSFET neuron circuit.

For the neuron circuits, the energy consumption, power consumption and energy efficiency are estimated from the following expressions;

For a single I&F operation, the MOSFET neuron circuit demands an energy consumption of 0.68 nJ with a power consumption of 19.1 μW and an energy efficiency of 33.0% at ISynaptic = 9.5 μA, tSynaptic = 1.2 μs, and the firing frequency = 28.1 kHz. In comparison with the MOSFET neuron circuit, the diode neuron circuit consumes much lesser power and energy for a single I&F operation; the energy consumption, power consumption and energy efficiency are 0.59 fJ, 16.7 pW and 96.3%, respectively, under the same conditions of ISynaptic as the MOSFET neuron circuit. The excellent power consumption and energy efficiency of the diode neuron circuit originate from the latch-up of the anode current and the high ratio (approximately 1013) of the anode current to the off current of the p-n-p-n diode. Therefore, the presented neuron circuit utilizing the p-n-p-n diode is superior in terms of the power consumption and energy efficiency in comparison with that constructed with only MOSFETs.

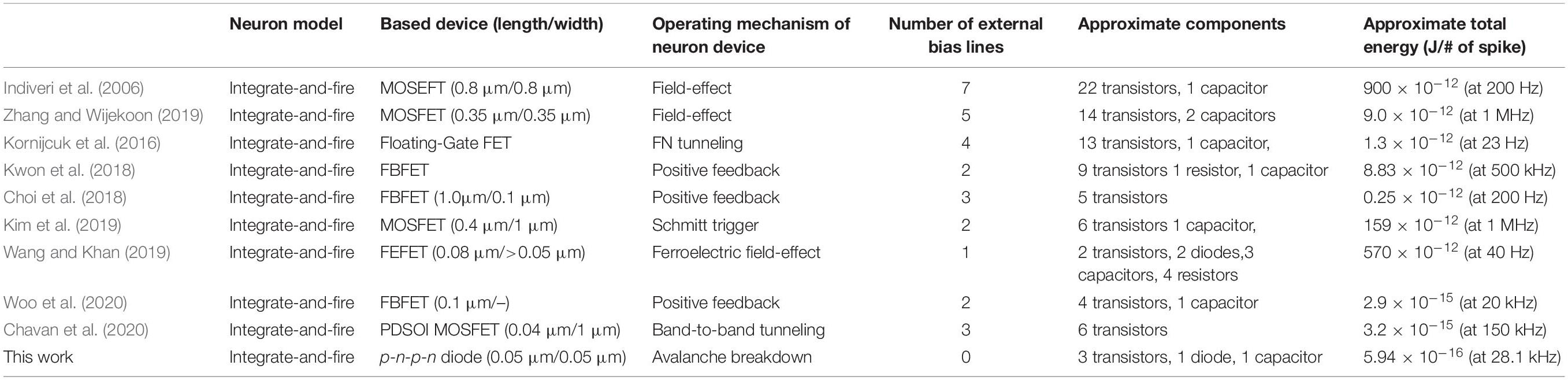

The diode neuron circuit is compared with other neuron circuits with respect to the device type, and the number of external bias lines, and components needed for I&F operations, as well as energy consumption. In Table 1, the CMOS, floating-gate FET and FBFET neuron circuits reported by other research groups require 5–23 elements with capacitors, and more than 1–10 external bias lines which require extra peripheral circuit for generating bias voltages, causing these neuron circuits to consume high power and energy (Indiveri et al., 2006; Kornijcuk et al., 2016; Choi et al., 2018; Kwon et al., 2018; Kim et al., 2019; Wang and Khan, 2019; Zhang and Wijekoon, 2019; Chavan et al., 2020; Woo et al., 2020). The FBFET neuron circuit has relatively low energy consumption compared to others except ours, but this neuron circuit requires extra peripheral circuits for generating voltage bias and controllers for the I&F operation (Choi et al., 2018; Kwon et al., 2018; Woo et al., 2020). The PDSOI MOS-based neuron circuit also requires an external reset circuit applied with changeable gate voltage to reset the membrane potential (Chavan et al., 2020). In contrast, the presented neuron circuit has only five components and requires no external bias lines. Consequently, this neuron circuit has the lowest energy consumption.

Table 1. Comparison of the presented neuron circuit with neuron circuits reported by other research groups regarding the based device types, number of external bias lines, and components as well as energy consumption.

The presented neuron circuit consisting of a p-n-p-n diode, a capacitor, and three transistors, with an energy consumption of 0.59 fJ and an energy efficiency of 96.3%, does not require any external bias lines for its I&F operation. In the I&F operation, the firing frequency can be adjusted by varying the amplitude and width of the synaptic current pulses. In comparison with CMOS-, FGFET-, and FBFET-based neuron circuits, the proposed circuit is much simpler, because of the absence of external bias lines and the use of the diode.

Moreover, the presented neuron circuit is superior in terms of the power consumption and energy efficiency in comparison with circuits constructed with only MOSFETs. This research demonstrates the possibility of neuromorphic computing architectures driven by SNNs without external bias lines.

The I&F neuron circuit was carried out with a two-dimensional device simulator (Silvaco Atlas, version 5.20.2 R) (Silvaco, 2016). In the simulation of the p-n-p-n diode, the BJT model and Fermi-Dirac statistics were employed to analyze the device characteristics, and the CVT transverse electric-field-dependent mobility of the charge carriers assumed in this work (Han and Choi, 2010). In the MOSFET simulation, the MOS2 model was used for analyzing. The default parameters for these models were used in the simulation.

All datasets generated for this study are included in the article/Supplementary Material, further inquiries can be directed to the corresponding author/s.

Y-SP, SW, and SK: conceptualization and data curation. Y-SP, DL, and SK: methodology. Y-SP and KC: validation and investigation. KC and SK: formal analysis. Y-SP and SK: resources, writing—review and editing, visualization, and project administration. Y-SP and SK: writing—original draft preparation. All authors have read and agreed to the published version of the manuscript and have cooperated in the preparation of this work.

This research was supported in part by the Ministry of Trade, Industry & Energy (MOTIE) (10067791) and Korea Semiconductor Research Consortium (KSRC) support program for the development of future semiconductor devices, in part by the National Research Foundation of Korea (NRF) grant funded by the Korea Government (MSIT) (2020R1A2C3004538), the Brain Korea 21 Plus Project of 2020 through the NRF funded by the Ministry of Science, and ICT & Future Planning, and the Korea University Grant.

The authors declare that the research was conducted in the absence of any commercial or financial relationships that could be construed as a potential conflict of interest.

The Supplementary Material for this article can be found online at: https://www.frontiersin.org/articles/10.3389/fnins.2021.644604/full#supplementary-material

Abbott, L. F. (1999). Lapicque’s introduction of the integrate-and-fire model neuron (1907). Brain Res. Bull. 50, 303–304. doi: 10.1016/s0361-9230(99)00161-6

Bear, M. F., Connors, B. W., and Paradiso, M. A. (2007). Neuroscience, Vol. 2. Philadelphia, PA: Lippincott Williams & Wilkins.

Chavan, T., Dutta, S., Mohapatra, N. R., and Ganguly, U. (2020). Band-to-band tunneling based ultra-energy-efficient silicon neuron. IEEE Trans. Electron Devices 67, 2614–2620. doi: 10.1109/ted.2020.2985167

Cheung, K. P. (2010). “On the 60 mV/dec@ 300 K limit for MOSFET subthreshold swing,” in Proceedings of the 2010 International Symposium on VLSI Technology, System and Application, (Hsinchu: IEEE), 72–73.

Choi, K. B., Woo, S. Y., Kang, W. M., Lee, S., Kim, C. H., Bae, J. H., et al. (2018). A split-gate positive feedback device with an integrate-and-fire capability for a high-density low-power neuron circuit. Front. Neurosci. 12:704. doi: 10.3389/fnins.2018.00704

Chu, M., Kim, B., Park, S., Hwang, H., Jeon, M., Lee, B. H., et al. (2014). Neuromorphic hardware system for visual pattern recognition with memristor array and CMOS neuron. IEEE Trans. Ind. Electron. 62, 2410–2419. doi: 10.1109/tie.2014.2356439

Han, J. W., and Choi, Y. K. (2010). Biristor—Bistable resistor based on a silicon nanowire. IEEE Electron Device Lett. 31, 797–799. doi: 10.1109/led.2010.2051405

Holonyak, N. (2001). The silicon pnpn switch and controlled rectifier (thyristor). IEEE Trans. Power Electronics 16, 8–16. doi: 10.1109/63.903984

Indiveri, G., Chicca, E., and Douglas, R. (2006). A VLSI array of low-power spiking neurons and bistable synapses with spike-timing dependent plasticity. IEEE Trans. Neural Netw. 17, 211–221. doi: 10.1109/tnn.2005.860850

Izhikevich, E. M. (2003). Simple model of spiking neurons. IEEE Trans. Neural Netw. 14, 1569–1572. doi: 10.1109/tnn.2003.820440

Kim, T., Song, Y. S., and Park, B. G. (2019). Overflow handling integrate-and-fire silicon-on-insulator neuron circuit incorporating a Schmitt trigger implemented by back-gate effect. J. Nanosci. Nanotechnol. 19, 6183–6186. doi: 10.1166/jnn.2019.17004

Kornijcuk, V., Lim, H., Seok, J. Y., Kim, G., Kim, S. K., Kim, I., et al. (2016). Leaky integrate-and-fire neuron circuit based on floating-gate integrator. Front. Neurosci. 10:212. doi: 10.3389/fnins.2016.00212

Kwon, M. W., Baek, M. H., Hwang, S., Park, K., Jang, T., Kim, T., et al. (2018). Integrate-and-fire neuron circuit using positive feedback field effect transistor for low power operation. J. Appl. Phys. 124:152107. doi: 10.1063/1.5031929

Lim, D., Kim, M., Kim, Y., and Kim, S. (2017). Memory characteristics of silicon nanowire transistors generated by weak impact ionization. Sci. Rep. 7:12436.

Merolla, P. A., Arthur, J. V., Alvarez-Icaza, R., Cassidy, A. S., Sawada, J., Akopyan, F., et al. (2014). A million spiking-neuron integrated circuit with a scalable communication network and interface. Science 345, 668–673. doi: 10.1126/science.1254642

Moll, J. L., Tanenbaum, M., Goldey, J. M., and Holonyak, N. (1956). PNPN transistor switches. Proc. IRE 44, 1174–1182.

Srinivasan, G., Roy, S., Raghunathan, V., and Roy, K. (2017). “Spike timing dependent plasticity based enhanced self-learning for efficient pattern recognition in spiking neural networks,” in Proceedings of the 2017 International Joint Conference on Neural Networks (IJCNN), (Anchorage, AK: IEEE), 1847–1854.

Wang, Z., and Khan, A. I. (2019). Ferroelectric relaxation oscillators and spiking neurons. IEEE J. Explor. Solid State Comput. Devices Circuits 5, 151–157. doi: 10.1109/jxcdc.2019.2928769

Woo, S., Cho, J., Lim, D., Park, Y. S., Cho, K., and Kim, S. (2020). Implementation and characterization of an integrate-and-fire neuron circuit using a silicon nanowire feedback field-effect transistor. IEEE Trans. Electron Devices 67, 2995–3000. doi: 10.1109/ted.2020.2995785

Xiaodong, T., Hao, W., Qingqing, L., Huicai, Z., Huilong, Z., Chao, Z., et al. (2014). Design of two-terminal PNPN diode for high-density and high-speed memory applications. J. Semiconductors 35:014006. doi: 10.1088/1674-4926/35/1/014006

Keywords: p-n-p-n diode, technology computer-aided design simulation, latch-up phenomenon, integrate-and-fire neuron, spiking neural networks, absence of external bias lines

Citation: Park Y-S, Woo W, Lim D, Cho K and Kim S (2021) Integrate-and-Fire Neuron Circuit Without External Bias Voltages. Front. Neurosci. 15:644604. doi: 10.3389/fnins.2021.644604

Received: 21 December 2020; Accepted: 03 March 2021;

Published: 24 March 2021.

Edited by:

Hong Qu, University of Electronic Science and Technology of China, ChinaReviewed by:

Robert W. Newcomb, University of Maryland, College Park, United StatesCopyright © 2021 Park, Woo, Lim, Cho and Kim. This is an open-access article distributed under the terms of the Creative Commons Attribution License (CC BY). The use, distribution or reproduction in other forums is permitted, provided the original author(s) and the copyright owner(s) are credited and that the original publication in this journal is cited, in accordance with accepted academic practice. No use, distribution or reproduction is permitted which does not comply with these terms.

*Correspondence: Sangsig Kim, c2FuZ3NpZ0Brb3JlYS5hYy5rcg==

Disclaimer: All claims expressed in this article are solely those of the authors and do not necessarily represent those of their affiliated organizations, or those of the publisher, the editors and the reviewers. Any product that may be evaluated in this article or claim that may be made by its manufacturer is not guaranteed or endorsed by the publisher.

Research integrity at Frontiers

Learn more about the work of our research integrity team to safeguard the quality of each article we publish.